## Digilent Arty A7-100T

# Digilent Arty A7-100T Artix-7 FPGA Development Board User Manual

Model: Arty A7-100T (410-319)

## 1. INTRODUCTION

The Digilent Arty A7-100T is a versatile Field Programmable Gate Array (FPGA) development board designed for makers and hobbyists. It features the Xilinx Artix-7 XC7A100TCSG324-1 FPGA, offering a powerful platform for digital circuit design, embedded systems development, and various custom hardware projects. This manual provides essential information for setting up, operating, and maintaining your Arty A7-100T board.

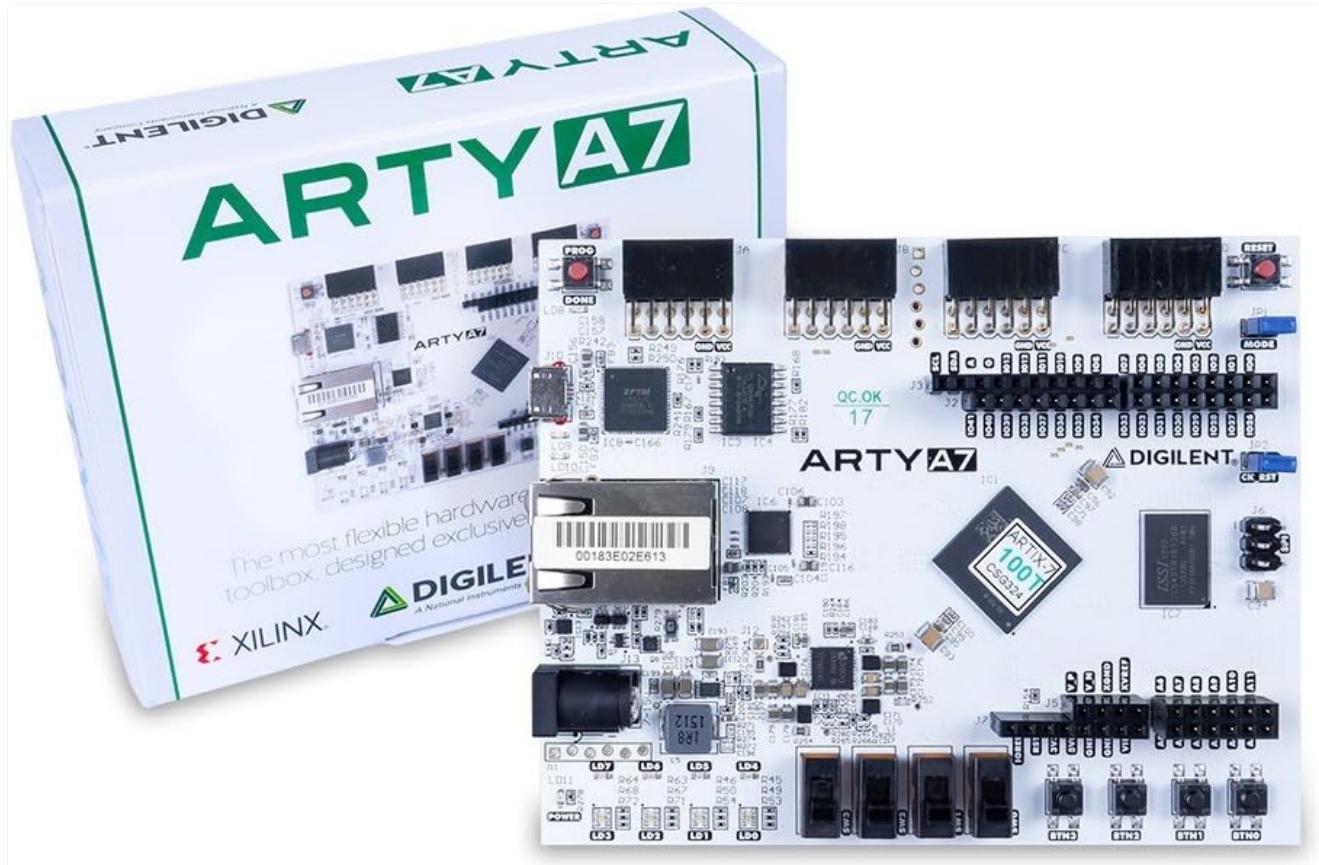

Figure 1: Digilent Arty A7-100T FPGA Development Board and its retail packaging.

## 2. KEY FEATURES

The Arty A7-100T board is equipped with a range of features to support diverse development needs:

- **FPGA:** Xilinx Artix-7 XC7A100TCSG324-1.

- **Clock Speed:** Internal clock speeds exceeding 450MHz.

- **Analog-to-Digital Converter:** On-chip XADC.

- **Programming:** Programmable over JTAG and Quad-SPI Flash.

- **Memory:** 256MB DDR3L with a 16-bit bus @ 667MHz, 16MB Quad-SPI Flash.

- **Connectivity:** 10/100 Mbps Ethernet, USB-UART Bridge.

- **Power:** Powered from USB or any 7V-15V source.

- **User Interfaces:** 4 Switches, 4 Buttons, 1 Reset Button, 4 LEDs, 4 RGB LEDs.

- **Expansion:** 4 Pmod connectors, shield connector.

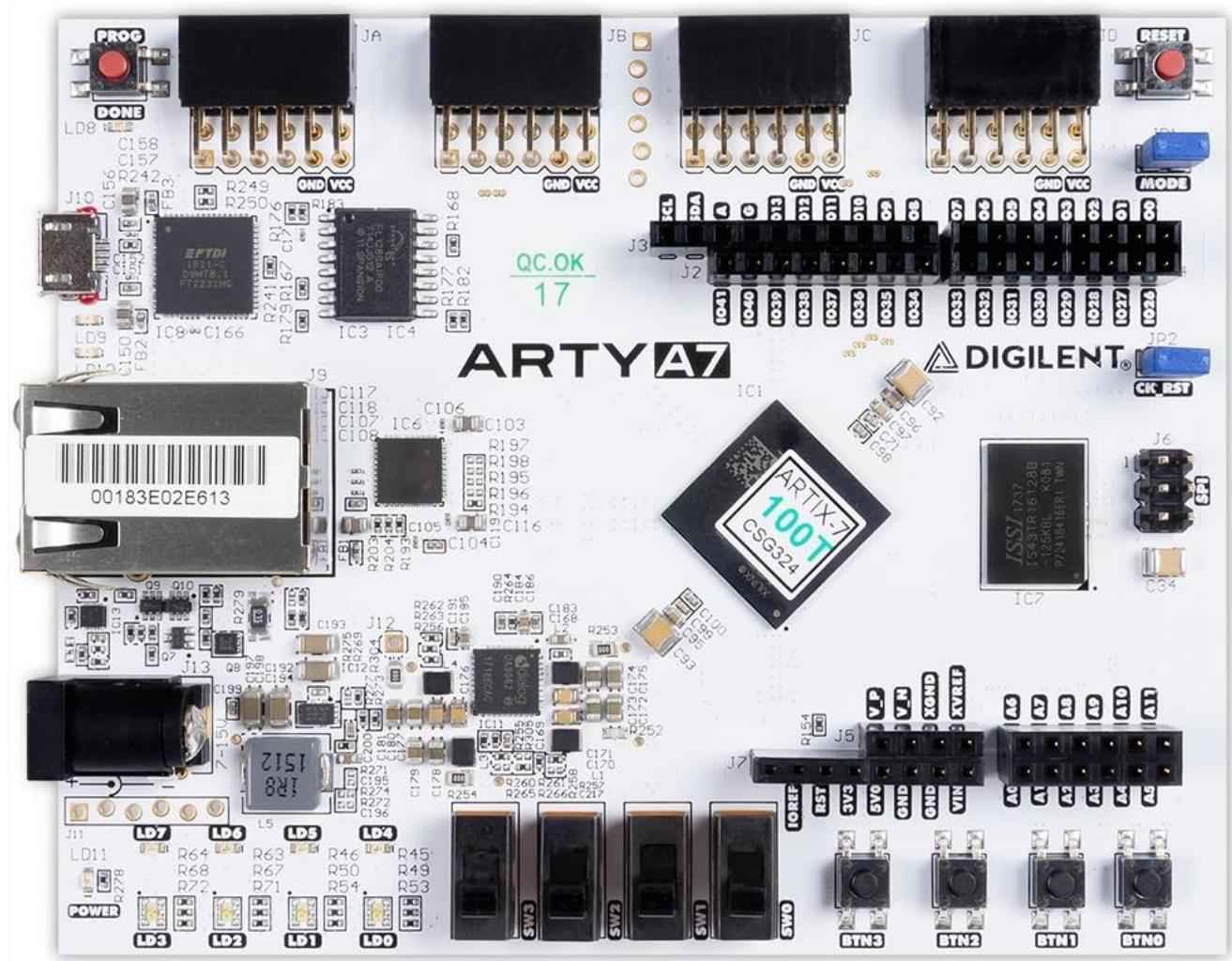

Figure 2: Top-down view of the Arty A7-100T board, highlighting the Artix-7 FPGA, Ethernet port, and various user I/O components.

## 3. SETUP GUIDE

Follow these steps to set up your Arty A7-100T development board:

### 1. Power Connection:

The Arty A7-100T can be powered via the USB port or an external 7V-15V DC power supply connected to the barrel jack. For initial setup and programming, connecting via USB is typically sufficient.

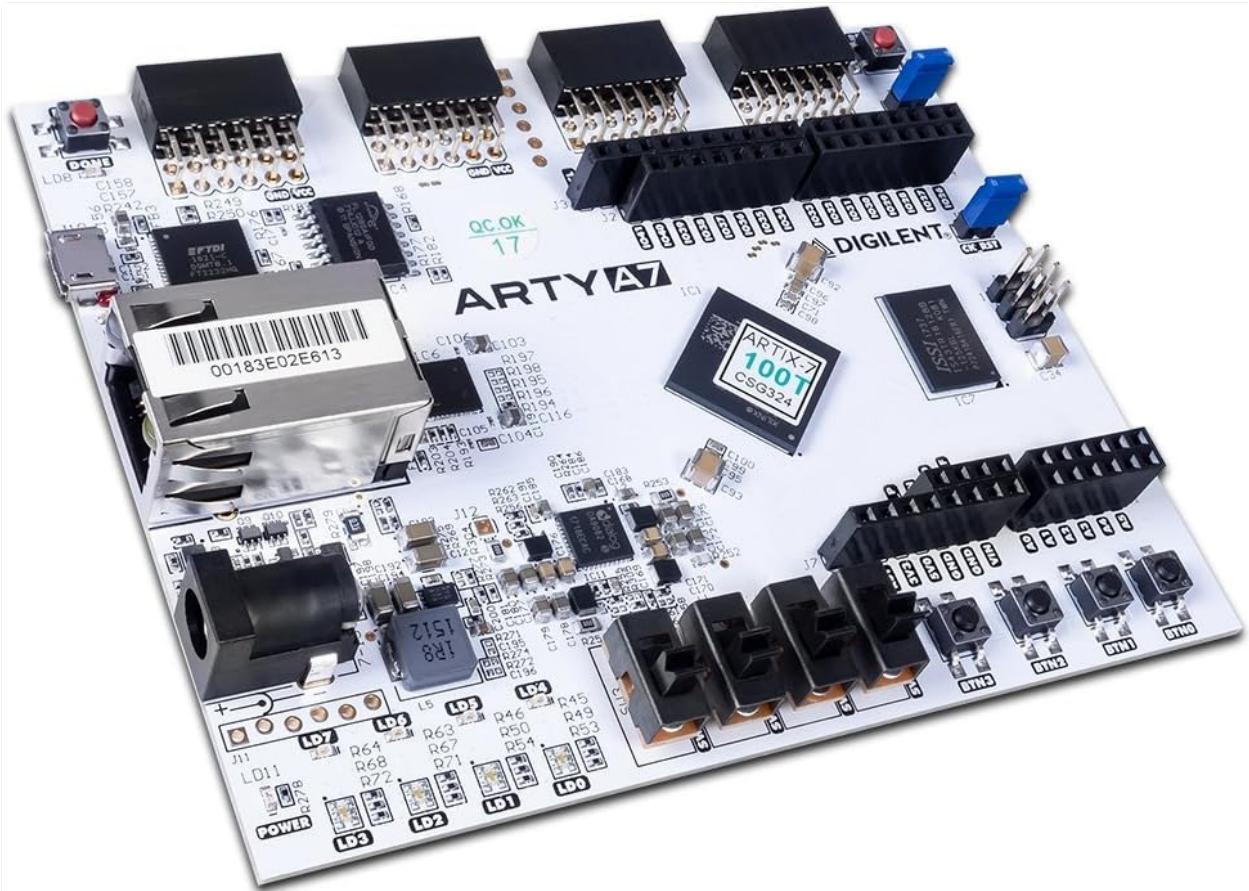

Figure 3: Angled view of the Arty A7-100T, showing the USB port and DC barrel jack for power input.

## 2. USB Connection:

Connect the Arty A7-100T to your computer using a USB cable. This connection provides power, enables USB-JTAG programming, and facilitates communication via the USB-UART bridge.

## 3. Software Installation:

Install the Xilinx Vivado Design Suite (WebPack edition is suitable for this board) on your computer. This software is required for developing, synthesizing, and programming your FPGA designs. Refer to the official Xilinx documentation for detailed installation instructions.

## 4. Driver Installation:

Ensure that the necessary USB drivers for the Digilent board are installed. These are typically included with the Vivado installation or can be downloaded from the Digilent website.

## 4. OPERATING INSTRUCTIONS

Operating the Arty A7-100T involves creating and deploying FPGA designs. Here's a general workflow:

### 1. Project Creation:

Start a new project in Xilinx Vivado. Select the correct FPGA part: **XC7A100TCSG324-1** (or **XC7A35TICSG324-1L** if you have the 35T variant).

### 2. Design Entry:

Write your hardware description language (HDL) code (VHDL or Verilog) for your desired functionality. This could involve implementing custom logic, a soft-core processor like MicroBlaze, or interfacing with peripherals.

### 3. Constraint Files (XDC):

Add Xilinx Design Constraint (XDC) files to map your design's I/O ports to the physical pins on the Arty A7-100T board. Digilent provides master XDC files for the Arty A7 on their website, which serve as a good starting point.

### 4. Synthesis and Implementation:

Run synthesis and implementation in Vivado. This process translates your HDL code into a netlist, maps it to the FPGA's resources, and generates the bitstream file.

#### 5. Bitstream Generation:

After successful implementation, generate the bitstream (.bit) file. This file contains the configuration data for the FPGA.

#### 6. Programming the FPGA:

Use the Vivado Hardware Manager to connect to your Arty A7-100T board via the USB-JTAG interface.

Program the FPGA with your generated bitstream. You can also program the Quad-SPI Flash for persistent storage of your design.

#### 7. Testing and Debugging:

Test your design using the onboard switches, buttons, and LEDs, or by connecting external Pmod modules.

Utilize Vivado's debugging tools, such as the Integrated Logic Analyzer (ILA), for verifying internal signals.

## 5. MAINTENANCE

---

Proper care and maintenance will ensure the longevity and reliable operation of your Arty A7-100T board:

- **Handling:** Always handle the board by its edges to avoid touching sensitive components.

- **Static Discharge:** Take precautions against electrostatic discharge (ESD) when handling the board. Use an anti-static wrist strap and work on an ESD-safe surface.

- **Cleaning:** Keep the board clean and free from dust and debris. Use compressed air or a soft brush for cleaning. Avoid using liquids directly on the board.

- **Storage:** Store the board in an anti-static bag when not in use, in a dry environment away from extreme temperatures.

- **Power Supply:** Use only recommended power supplies (USB or 7V-15V DC). Incorrect voltage can damage the board.

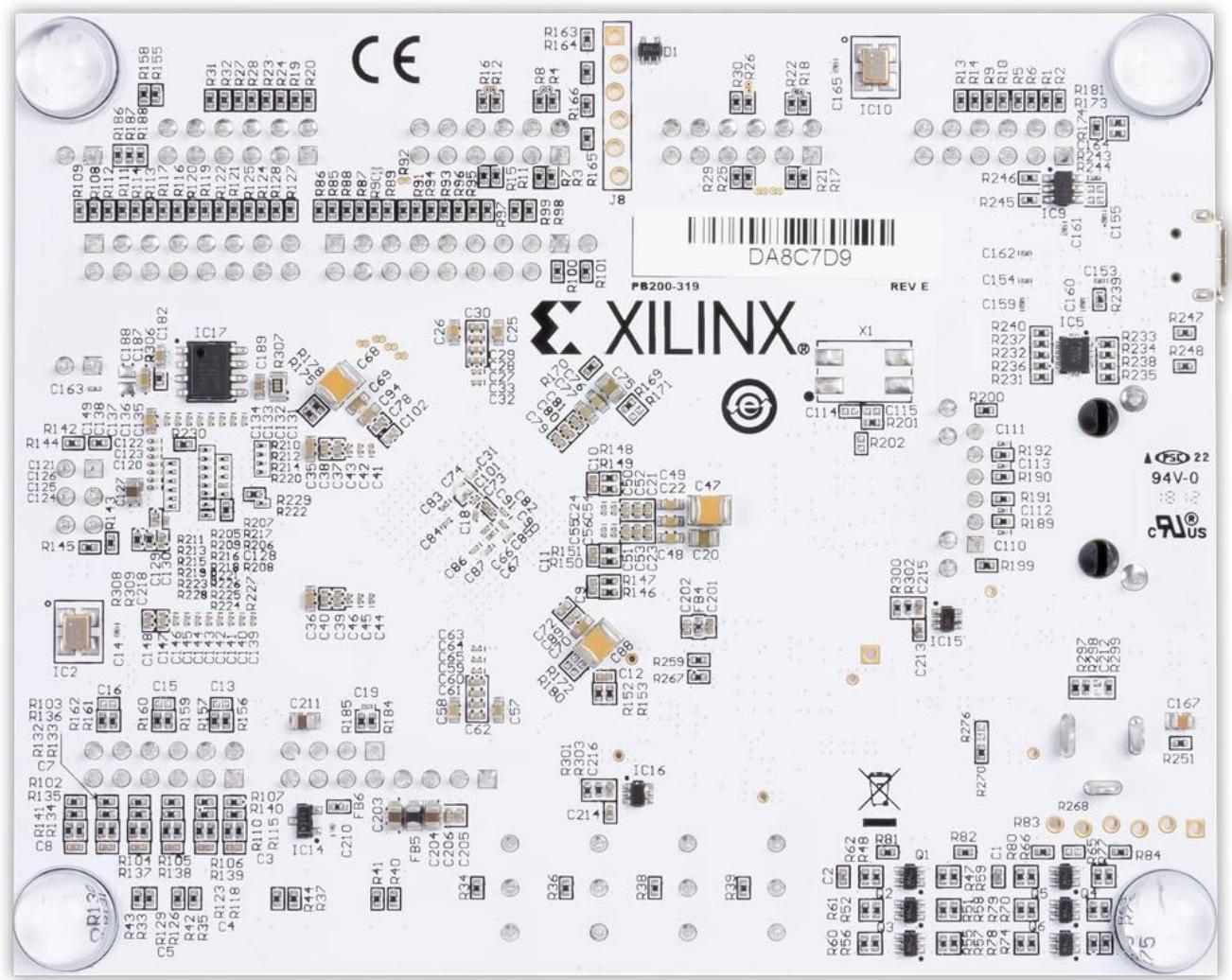

Figure 4: Bottom view of the Arty A7-100T board, showing solder points and regulatory markings.

## 6. TROUBLESHOOTING

If you encounter issues with your Arty A7-100T, consider the following troubleshooting steps:

- **Power Indicator:** Check if the power LED (LD1) is illuminated when the board is connected to power. If not, verify your power source and connections.

- **USB Connection Issues:** If your computer does not recognize the board, ensure USB drivers are correctly installed. Try a different USB port or cable.

- **Programming Errors:**

- Verify that the correct FPGA part (XC7A100TCSG324-1) is selected in your Vivado project.

- Ensure the JTAG chain is correctly detected in Vivado Hardware Manager.

- Check for any error messages in the Vivado console.

- **Design Functionality:**

- Double-check your HDL code for syntax or logical errors.

- Review your XDC constraints to ensure correct pin assignments.

- Use Vivado's simulation tools to verify your design logic before programming the FPGA.

- Utilize the Integrated Logic Analyzer (ILA) for on-chip debugging of your running design.

- **External Peripherals:** If using Pmod connectors, ensure they are correctly connected and compatible with the Arty A7's voltage levels and pin assignments.

## 7. SPECIFICATIONS

|                                   |                                 |

|-----------------------------------|---------------------------------|

| <b>FPGA Model</b>                 | Xilinx Artix-7 XC7A100TCSG324-1 |

| <b>RAM Memory Installed Size</b>  | 256 MB DDR3L                    |

| <b>Flash Memory</b>               | 16 MB Quad-SPI Flash            |

| <b>CPU Speed (Internal Clock)</b> | Exceeding 450 MHz               |

| <b>Ethernet</b>                   | 10/100 Mbps                     |

| <b>Power Input</b>                | USB or 7V-15V DC                |

| <b>Package Dimensions</b>         | 4.41 x 3.54 x 1.26 inches       |

| <b>Item Weight</b>                | 11.3 ounces                     |

| <b>Model Number</b>               | 410-319                         |

| <b>Manufacturer</b>               | Digilent                        |

## 8. WARRANTY AND SUPPORT

The Digilent Arty A7-100T is manufactured by Digilent. For detailed warranty information, technical support, and additional resources such as schematics, reference manuals, and example projects, please visit the official Digilent website.

[Visit Digilent's Official Website](#)

### Related Documents - Arty A7-100T

|                                                                                     |                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p><a href="#">Digilent CoolRunner-II Starter Board Reference Manual</a></p> <p>A comprehensive reference manual for the Digilent CoolRunner-II Starter Board, a USB-powered development platform featuring a Xilinx CoolRunner-II CPLD, power supplies, oscillator, I/O devices, and expansion connectors.</p> |

|  | <p><a href="#">Digilent FX12 Board Errata and Modifications</a></p> <p>Official errata document from Digilent detailing modifications made to the FX12 development board, specifically addressing JTAG signal routing issues on Rev B boards.</p>                                                               |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | <p><a href="#">Digilent Pmod 8LD Reference Manual - High-Brightness LED Module</a></p> <p>Detailed reference manual for the Digilent Pmod 8LD, a compact module featuring eight high-brightness green LEDs controlled via GPIO pins and BJTs for low-power logic-level operation.</p>                                                                                                                                                                          |

|   | <p><a href="#">Digilent PmodIOXP Input/Output Expansion Module Reference Manual</a></p> <p>This reference manual details the Digilent PmodIOXP, an Input/Output expansion module designed to provide up to 19 additional I/O pins. It highlights features such as I<sup>2</sup>C communication, a 16-element FIFO, built-in keypad decoding, and PWM generation, along with functional descriptions, interfacing details, pinout, and physical dimensions.</p> |

|   | <p><a href="#">Digilent PmodDHB1 Dual H-Bridge Motor Driver Reference Manual</a></p> <p>Reference manual for the Digilent PmodDHB1, a dual H-bridge motor driver capable of controlling two DC motors or a bipolar stepper motor, featuring over-current protection and quadrature encoder feedback.</p>                                                                                                                                                       |

|  | <p><a href="#">Digilent PmodRS485 Reference Manual</a></p> <p>This reference manual provides detailed information on the Digilent PmodRS485, a high-speed RS-485 communication module offering signal and power isolation for robust data transfer in noisy environments. It covers features, functional description, interfacing, pinouts, and physical dimensions.</p>                                                                                       |

Documents - Digilent – Arty A7-100T

**DIGILENT**

An NI Company

320 Henley Court

Pullman, WA 99163

509.334.6306

www.digilent.com

**Arty A7-100T™ Statement of Volatility**

Revised April 27, 2023 Author: AB

This document lists the location, purpose, capacity, volatility, and reprogrammability of memory devices that may be included in the Arty A7-100T. The Arty A7-100T is a high-performance, high-density, and low-power FPGA. It is a device that is not intended for use in medical, safety, or other applications where failure of the device could result in personal injury or death. The Arty A7-100T is a device that is not intended for use in medical, safety, or other applications where failure of the device could result in personal injury or death. The Arty A7-100T is a device that is not intended for use in medical, safety, or other applications where failure of the device could result in personal injury or death. The Arty A7-100T is a device that is not intended for use in medical, safety, or other applications where failure of the device could result in personal injury or death.

The content of this document is provided for information purposes only.

**Volatile Memory**

|                  | Memory Region                      | User programmable | User removable | SRAM            | Flash                       | Reset procedure |

|------------------|------------------------------------|-------------------|----------------|-----------------|-----------------------------|-----------------|

| XC7A200T-2SGG324 | DS91 Program/ User memory          | Yes               | No             | 256b            | Retain power for 10 seconds |                 |

| XC7A200T-2SGG324 | Configurable SRAM for interconnect | Yes               | No             | 32,400,480 bits | Retain power for 10 seconds |                 |

| XC7A200T-2SGG324 | Block RAM                          | Yes               | No             | 4,096 bits      | Retain power for 10 seconds |                 |

| XC7A200T-2SGG324 | Configurable RAM                   | Yes               | No             | 1,389,110 bits  | Retain power for 10 seconds |                 |

Page 2 of 2

[\[pdf\]](#)

Norman MacDonald Arty A7 100T RevE SoV files digilent resources programmable logic arty a7 |||

**Arty A7-100TTM Statement of Volatility Revised April 27, 2023 Author: AB**

This document applies to the Arty A7 rev. E.X 1300 Henley Court Pullman, WA 99163

509.334.6306 www.digilent.com This document lists the location, purpose, capacity, volatility and re programmability of memory devices that ma...

lang:en score:43 filesize: 160.44 K page\_count: 2 document date: 2023-04-27

**DIGILENT**

A National Instruments Company

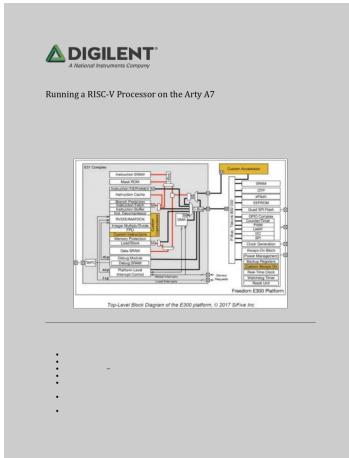

**Running a RISC-V Processor on the Arty A7**

The Arty A7-100T contains a Xilinx XC7A100T FPGA which is the largest FPGA available for the Arty A7 and is ideal for deployment of softcore processors. These processors can be either proprietary or open source. One of the most popular open source processors is the RISC-V. This tutorial covers building a RISC-V processor, specifically the SiFive Freedom E310. This guide steps through the process of loading the Freedom E310 onto an Arty A7, and programming it using the Arduino IDE.

This tutorial covers building a RISC-V processor, specifically the SiFive Freedom E310 and steps through the process of loading the Freedom E310 onto an Arty A7, and programming it using the Arduino IDE.

- Getting Started

- Building the RISC-V

- Programming the Hardware

- Generating Software

What do you need for this project?

- Arty A7-100T

- Ubuntu 18.04 LTS 64bit

- SiFive RISC-V USB Programmer

- Ubuntu 20.04 LTS - Wikipedia Edition

- Arduino Dev Segment Environment

- SiFive RISC-V USB Programmer and the programmer and use of the Arty's Pmod connectors, which is connected to the JTAG Test Access Port of the processor.

- A Linux development or virtual machine is needed to compile the processor, generate the firmware and update metadata to the processor.

With the following tutorial at [https://reference.digilentinc.com/reference/programmable\\_hardware/arty\\_a7\\_100t\\_risc\\_v/](https://reference.digilentinc.com/reference/programmable_hardware/arty_a7_100t_risc_v/) to create the RISC-V based application

www.digilentinc.com

[\[pdf\]](#) Quick Start Guide Guide

Microsoft Word Running a RISC V Processor on Arty A7 100T joe wilkins Development Board Digilent Mouser RunningaRISCVProcessoronArtyA7 mouser be Docs |||

Running a RISC-V Processor on the Arty A7 The Arty A7-100T contains a Xilinx XC7A100T FPGA which is the largest FPGA available for the Arty A7 and is ideal for deployment of softcore processors. These processors can be either proprietary or open source. One of the most popular open source processors...

lang:en score:36 filesize: 492.18 K page\_count: 1 document date: 2020-03-17

SiFive

From a Custom 2 Series Core to Hello World in 30 Minutes

Drew Barbier - Sr. Product Marketing Manager Amy Lindburg - Director Product Management May, 2019

[\[pdf\]](#) User Manual Guide

Minutes From a Custom 2 Series Core to Hello World in 30 Manual functional description of the deliverable User Guide detailed including information on integration and testbench Arty FPGA describes how use info Metadata about design device tree retiming SiFive Insight tests sifive cdn prismic io 79079c42 21c9 4829 a7f9 eaa565673bf3

From a Custom 2 Series Core to Hello World in 30 Minutes Drew Barbier - Sr. Product Marketing Manager Amy Lindburg - Director Product Management May, 2019 About This Presentation This presentation will introduce SiFive Core Designer, our RISC-V Core IP deliverables, and software development method...

lang:en score:35 filesize: 1.88 M page\_count: 22 document date: 0000-00-00

## [\[pdf\] Installation Guide Guide Declaration of Conformity](#)

Running a RISC V Processor on the Arty A7 media digikey Other Related Documents Digilent Doc |||

Running a RISC-V Processor on the Arty A7 The Arty A7-100T contains a Xilinx XC7A100T FPGA which is the largest FPGA available for the Arty A7 and is ideal for deployment of softcore processors. These processors can be either proprietary or open source. One of the most popular open source processors...

lang:en score:32 filesize: 915.45 K page\_count: 8 document date: 2020-03-09

## [\[pdf\] Quick Start Guide Instructions Guide](#)

Introduction SiFive Core IP FPGA Eval Kit User Guide Version Prismic If using cJTAG please see additional instructions in Freedom E SDK Section 7 Page 11 Note It is important to connect PMOD header JD not fpga getting started v2019p05 sifive cdn prismic io a76dc011 5d11 4d73 9e7a 900640d76f3d

SiFive Core IP FPGA Eval Kit User Guide Version v2019p05 SiFive, Inc. SiFive Core IP FPGA Eval Kit ... ts: The Arty A7-35T features Xilinx XC7A35TICSG324-1L. This board is no longer fully supported. The Arty A7-100T features the larger Xilinx XC7A100TCSG324-1. This is the suggested board for SiFive Cor...

lang:en score:29 filesize: 1.34 M page\_count: 40 document date: 2019-06-21

## [\[pdf\]](#)

Elod Gyorgy S25FL127S PCN files digilent resources programmable logic documents |||

PCN Due to supply chain constraints, the Spansion/Infineon/Cypress

S25FL128SAGMFx00 is being supplemented with the Spansion/Infineon/Cypress S25FL127SABMFx00x on several Digilent products starting the PCA revisions listed in the table below. Affected articles will have a sticker placed on the PCB w...

lang:en score:28 filesize: 83.48 K page\_count: 1 document date: 2022-03-17

### [\[pdf\]](#) Datasheet

Datasheet Digilent 410 352 25 Embedded Processors and Controllers IBS Electronics datasheet octopart 179056676 |||

FREE US shipping on orders 35 Home / FPGA Boards / Development Boards / Arty

S7: Spartan-7 FPGA D ... Zynq-7000 SoC Development Board 249.00 - 299.00

Digilent USB A to Micro-B Cable 4.99 Digilent Arty A7-100T: Artix-7 FPGA

Development Board 299.00 Digilent 6-pin Header Gender Changer 5- pac...

lang:en score:27 filesize: 2.16 M page\_count: 5 document date: 2024-01-22

### [\[pdf\]](#) Guide

SiFive Core IP FPGA Eval Kit User Guide v3p0 Signal Name ARM USB TINY H Pin Number Suggested Jumper Color Freedom E310 Arty coreip arty userguide sifive cdn prismic io e44a9cd4 7d5a 4dcf 9b4f d456887bd50b

SiFive Core IP FPGA Eval Kit User Guide v3p0 SiFive, Inc. 2 SiFive Core IP FPGA Eval Kit User Gu ... sts. The Arty A7 comes in two FPGA variants: The Arty A7-35T features Xilinx XC7A35TCSG324-1L. The Arty A7-100T features the larger Xilinx XC7A100TCSG324-1. Both can be purchased from Digilent or Avn...

lang:en score:21 filesize: 2.16 M page\_count: 41 document date: 2019-03-01

## [\[pdf\] Guide](#)

Introduction coreip fpga eval userguide v19 08 sifive cdn prismic io f290f543 87e9 4e0b 8a4a

6287217f79bc

SiFive Core IP FPGA Eval Kit User Guide Version v19.08p0 SiFive, Inc. SiFive Core IP FPGA Eval Kit ... ts: The Arty A7-35T features Xilinx XC7A35TCSG324-1L. This board is no longer fully supported. The Arty A7-100T features the larger Xilinx XC7A100TCSG324-1. This is the suggested board for SiFive Cor...

lang:en **score:11** filesize: 1.34 M page\_count: 40 document date: 2019-09-25

## [\[pdf\] Catalog](#)

DEVELOPMENT TOOLS catalog tme eu de catalogue DEVTOOLS22 EN html |||

8051 AVR PIC DSPIC ARM FPGA x86 tme.eu tme.com EMBEDDED SYSTEMS USB ETHERNET WI-FI BLUETOOTH ... 46-20 Manufacturer Manufacturer s symbol

Components DIGILENT ARTY S7-50 XC7S50-CSGA324 DIGILENT **ARTY A7-100T** XC7A100TCSG324-1 DIGILENT ARTY A7-35T XC7A35T-L1CSG324 DIGILENT ARTY Z7-20 XC7Z020...

lang:en **score:9** filesize: 17.6 M page\_count: 52 document date: 2023-06-09