## ArteryTek AT32F403AVGT7 32 Bit Microcontrollers User **Manual**

Home » ARTERYTEK » ArteryTek AT32F403AVGT7 32 Bit Microcontrollers User Manual

#### **Contents**

- 1 ArteryTek AT32F403AVGT7 32 Bit

- **Microcontrollers**

- **2 Product Usage Instructions**

- **3 Overview**

- 4 Quick start

- **5 Hardware and layout**

- **5.1 Power supply selection**

- 5.2 Programming and debugging

- 5.3 External clock source

- 6 Schematic

- 7 Revision history

- 8 Documents / Resources

- 8.1 References

- 9 Related Posts

# **ArteryTek**

## ArteryTek AT32F403AVGT7 32 Bit Microcontrollers

#### **Product Information**

The AT-START-F403A is an evaluation board based on the AT32F403AVGT7 chip. It features LED indicators, buttons, a USB micro-B connector, an Arduino Uno R3 extension connector, and an expanded 16 MB SPI Flash memory. This evaluation board includes the debugging/programming tool AT-Link-EZ, eliminating the need for additional development tools.

#### **Product Usage Instructions**

#### **Quick Start**

To get started with the AT-START-F403A, follow these steps:

- 1. Connect the power supply to the board.

- 2. Ensure the IDD (Input Device Description) is properly configured.

- 3. Program and debug the board using the embedded AT-Link-EZ tool.

- 4. Select the desired boot mode.

- 5. If necessary, connect an external clock source.

- 6. Utilize the LED indicators and buttons as needed.

- 7. Connect the board to a USB device if required.

- 8. Access Bank3 of Flash memory via the SPIM interface if needed.

- 9. Make use of the available 0 resistors as required.

- 10. Utilize the extension connectors, such as the Arduino Uno R3 extension connector, for additional functionality.

#### **Toolchains Supporting AT-START-F403A**

The AT-START-F403A is compatible with various toolchains that support its functionalities. Refer to the product documentation or website for a list of supported toolchains and their corresponding instructions.

#### **Hardware and Layout**

The user manual provides detailed information about the hardware and layout of the AT-START-F403A board. It covers topics such as power supply selection, IDD configuration, programming and debugging using AT-Link-EZ, boot mode selection, external clock source options, LED indicators, buttons, USB device connection, Flash memory access via SPIM interface, 0 resistors usage, and extension connector details.

For more information and specific instructions on each topic, refer to the AT-START-F403A User Manual available on the official website.

#### Introduction

AT-START-F403A is designed to help you explore the high-performance features of the 32-bit microcontroller, AT32F403A embedded with ARM Cortex®-M4F with FPU, and help develop your applications. AT-START-F403A is an evaluation board based on AT32F403AVGT7 chip with LED indicators, buttons, an USB micro-B connector, ArduinoTM Uno R3 extension connector and an expanded 16 MB SPI Flash memory. This evaluation board embeds debugging/programming tool AT-Link-EZ without the need of other development tools.

#### Overview

#### **Features**

AT-START-F403A has the following characteristics:

- AT-START-F403A has an on-board AT32F403AVGT7 microcontroller that embeds ARM Cortex®-M4F, 32-bit processor, 1024 KB Flash memory and 96+128 KB SRAM, LQFP100 packages.

- · On-board AT-Link connector:

- The on-board AT-Link-EZ can be used for programming and debugging (AT-Link-EZ is a simplified version of AT-Link, and does not support offline mode)

- If AT-Link-EZ is separated from this board by bending over along the joint, AT-START-F403A can be connected to an independent AT-Link for programming and debugging

- On-board 20-pin ARM standard JTAG connector (with a JTAG/SWD connector for programming/debugging)

- 16 MB SPI Flash EN25QH128A is used as an expanded Flash memory Bank 3

- · Various power supply methods:

- Through the USB bus of AT-Link-EZ

- Through the USB bus (VBUS) of AT-START-F403A

- External 7~12 V power supply (VIN)

- External 5 V power supply (E5V)

- External 3.3 V power supply

- 4 x LED indicators:

- LED1 (red) used for 3.3 V power-on

- 3 x user LED indicators: LED2 (red) LED3 (yellow) and LED4 (green)

- 2 x buttons (user button and reset button)

- 8 MHz HSE crystal

- 32.768 kHz LSE crystal

- · USB micro-B connector

- Various extension connectors can be quickly connected into a prototype board and easy to explore:

- ArduinoTM Uno R3 extension connector

- LQFP100 I/O extension connector

#### **Definition of terms**

- Jumper JPx ON

- Jumper installed

- Jumper JPx OFF Jumped not installed

- Resistor Rx ON

- Short by solder or  $0\Omega$  resistor

- · Resistor Rx OFF

Open

#### **Quick start**

AT-START-F403A is a low-cost and easy-to-use development kit that is designed for quickly evaluating and using the high-performance AT32F403A microcontrollers to develop applications.

#### **Get started**

Configure the AT-START-F403A board in the following order to start the application:

1. Check the Jumper position on the board:

JP1 is connected to GND or OFF (BOOT0 is 0, and BOOT0 has an pull-down resistor in the AT32F403AVGT7); JP4 optional or OFF (BOOT1 is in any state);

JP8 one-piece jumper is connected to I/O on the right.

- 2. Connect the AT-START-F403A board to the PC through an USB cable (Type A to micro-B), and the board will be powered via AT-Link-EZ USB connector CN6. LED1 (red) is always on, and the other three LEDs (LED2 to LED4) start to blink in turn.

- 3. After pressing the USER button (B2), the blink frequency of three LEDs are changed.

## **Toolchains supporting AT-START-F403A**

ARM® Keil®: MDK-ARM™

IAR™: EWARM

#### Hardware and layout

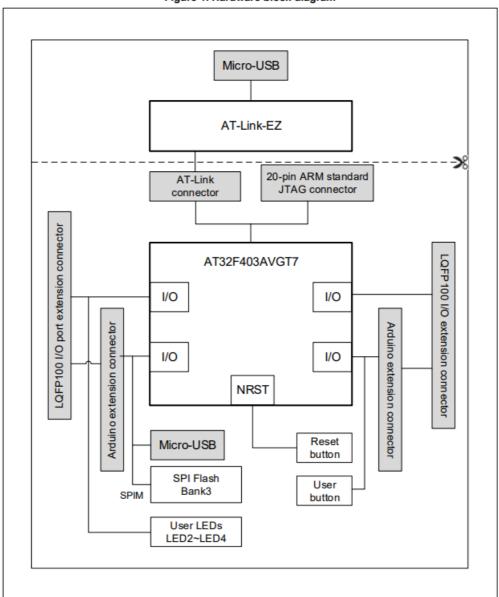

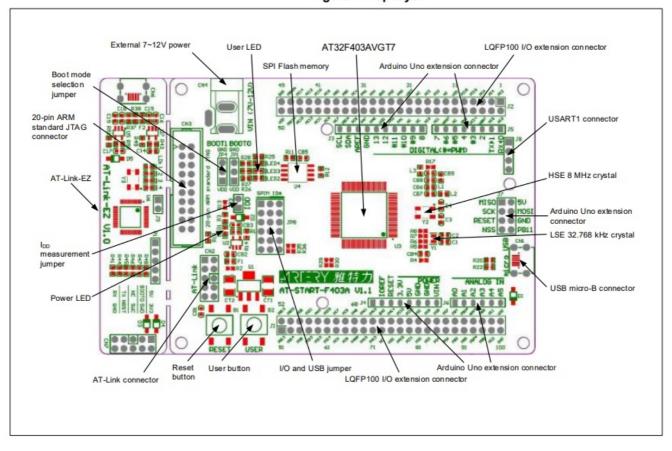

AT-START-F403A board is designed around an AT32F403AVGT7 microcontroller in LQFP100 package. **Figure 1** shows the connections between AT-Link-EZ, AT32F403AVGT7 and their peripherals (buttons, LEDs, USB, SPI Flash memory and extension connectors)

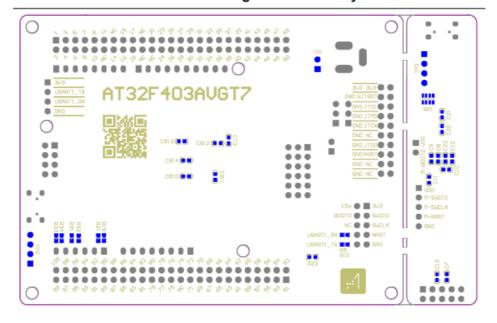

Figure 2 and Figure 3 show these features on the AT-Link-EZ and AT-START-F403A board.

Figure 1. Hardware block diagram

Figure 2. Top layer

Figure 3. Bottom layer

### Power supply selection

The 5 V power supply of AT-START-F403A can be provided through a USB cable (either through the USB connector CN6 on the AT-Link-EZ or USB connector CN1 on the AT-START-F403A), or through an external 5 V power supply (E5V), or by an external 7~12 V power supply (VIN) via 5V voltage regulator (U1) on the board. In this case, the 5 V power supply provides the 3.3 V power required by the microcontrollers and peripherals by means of the 3.3 V voltage regulator (U2) on the board.

The 5 V pin of J4 or J7 can also be used as an input power source. The AT-START-F403A board must be powered by a 5 V power supply unit.

The 3.3 V pin of J4 or the VDD pin of J1 and J2 can also be directly used as 3.3 V input power supply. AT-START-F403A board must be powered by a 3.3 V power supply unit.

#### Note:

Unless 5 V is provided through the USB connector (CN6) on the AT-Link-EZ, the AT-Link-EZ will not be powered by other power supply methods.

When another application board is connected to J4, the VIN, 5 V and 3.3 V pins can be used as output power; J7 5V pin used as 5 V output power; the VDD pin of J1 and J2 used as 3.3 V output power.

#### **IDD**

In the event of JP3 OFF (symbol IDD) and R13 OFF, it is allowed to connect an ammeter to measure the power consumption of AT32F403AVGT7.

• JP3 OFF, R13 ON:

AT32F403AVGT7 is powered. (Default setting and JP3 plug is not mounted before shipping)

• JP3 ON, R13 OFF:

AT32F403AVGT7 is powered.

• JP3 OFF, R13 OFF:

An ammeter must be connected to measure the power consumption of AT32F403AVGT7 (if there is no ammeter, the AT32F403AVGT7 cannot be powered).

#### Programming and debugging

#### **Embedded AT-Link-EZ**

The evaluation board embeds Artery AT-Link-EZ programming and debugging tool for users to program/debug the AT32F403AVGT7 on the AT-START-F403A board. AT-Link-EZ supports SWD interface mode and supports a set of virtual COM ports (VCP) to connect to the USART1\_TX/USART1\_RX (PA9/PA10) of AT32F403AVGT7. In this case, PA9 and PA10 of AT32F403AVGT7 will be affected by AT-Link-EZ as follows:

- PA9 is weakly pulled up to high level by the VCP RX pin of AT-Link-EZ;

- PA10 is strongly pulled up to high level by the VCP TX pin of AT-Link-EZ

The user can set R9 and R10 OFF, then the use of PA9 and PA10 of AT32F403AVGT7 is not subject to the above restrictions.

Please refer to AT-Link User Manual for complete details on the operations, firmware upgrade and precautions of AT-Link-EZ.

The AT-Link-EZ PCB on the evaluation board can be separated from AT-START-F403A by bending over along the joint. In this case, AT-START-F403A can still be connected to the CN7 of AT-Link-EZ through CN2 (not mounted before shipping), or can be connected with another AT-Link to continue the programming and debugging on the AT32F403AVGT7.

#### 20-pin ARM® standard JTAG connector

AT-START-F403A also reserves JTAG or SWD general-purpose connectors as programming/debugging tools. If the user wants to use this interface to program and debug the AT32F403AVGT7, please separate the AT-Link-EZ from the board or set R41, R44 and R46 OFF, and connect the CN3 (not mounted before shipping) to the programming and debugging tool.

#### **Boot mode selection**

At startup, three different boot modes can be selected by means of the pin configuration.

|                                                     | Boot mode selection |       |                                                                |  |

|-----------------------------------------------------|---------------------|-------|----------------------------------------------------------------|--|

| Jumper                                              | воот1               | воото | Setting                                                        |  |

| JP1 connected to GND or OFF;<br>JP4 optional or OFF | x                   | 0     | Boot from the internal Flash memory (Factory de fault setting) |  |

| JP1 connected to VDD JP4 connected to GND           | 0                   | 1     | Boot from the system memory                                    |  |

| JP1 connected to VDD JP4 connected to VDD           | 1                   | 1     | Boot from SRAM                                                 |  |

#### **External clock source**

#### **HSE clock source**

The 8 MHz crystal on the board is used as HSE clock source.

#### LSE clock source

There are three hardware modes to set the external low-speed clock sources:

• On-board crystal (default setting):

The 32.768 kHz crystal on the board is used as LSE clock source. The hardware setting must be: R6 and R7 ON, R5 and R8 OFF

• Oscillator from external PC14:

External oscillator is injected from the pin-3 of J2. The hardware setting must be: R5 and R8 ON, R6 and R7 OFF.

· LSE not used:

PC14 and PC15 are used as GPIO. The hardware setting must be: R5 and R8 ON, R6 and R7 OFF.

#### **LED** indicators

• Power LED1

Red indicates that the board is powered by 3.3 V

• User LED2

Red, connected to the PD13 pin of AT32F403AVGT7

• User LED3

Yellow, connected to the PD14 pin of AT32F403AVGT7

User LED4

Green, connected to the PD15 pin of AT32F403AVGT7

#### **Buttons**

• Reset button B1:

Connected to NRST to reset AT32F403AVGT7

• User button B2:

It is, by default, connected to the PA0 of AT32F403AVGT7, and alternatively used as a wakeup button (R19 ON, R21 OFF); or connected to PC13 and alternatively used as TAMPER-RTC button (R19 OFF, R21 ON)

#### **USB** device

AT-START-F403A board supports USB full-speed device communication through an USB micro-B connector (CN1). VBUS can be used as 5 V power supply of AT-START-F403A board.

## Connect to Bank3 of Flash memory via SPIM interface

The SPI Flash EN25QH128A on the board is connected to the AT32F403AVGT7 via SPIM interface and used as Bank 3 of expanded Flash memory.

When using the Bank 3 of the Flash memory via SPIM interface, the JP8 one-piece jumper, as shown in Table 2, should select the left SPIM side. In this case, PB1, PA8, PB10 PB11, PB6 and PB7 are not connected to the external LQFP100 I/O extension connector. These 6 pins are marked by adding [\*] after pin name of extension connector on the PCB silkscreen.

Table 2. GPIO and SPIM jumper setting

| Jumper                | Settings                                            |

|-----------------------|-----------------------------------------------------|

| JP8 connected to I/O  | Use I/O function (Default setting before shipping). |

| JP8 connected to SPIM | Use the SPIM function                               |

#### $0 \Omega$ resistors

**Table 3.**  $0 \Omega$  resistor setting

| State(1)        | Description                                                                                                                                                         |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ON              | When JP3 is OFF, 3.3V is connected to the microcontroller to provide power supply                                                                                   |  |  |

| OFF             | When JP3 is OFF, 3.3V allows an ammeter to be connected to measure the power consumption of microcontroller  (if no ammeter, the microcontroller cannot be powered) |  |  |

| ON              | VBAT must be connected to VDD                                                                                                                                       |  |  |

| OFF             | VBAT can be powered by the pin_6 VBAT of J2                                                                                                                         |  |  |

| OFF, ON, ON, OF | LSE clock source uses crystal Y1 on the board                                                                                                                       |  |  |

|                 | ON OFF ON OFF, ON, ON, OF                                                                                                                                           |  |  |

| R5, R6, R7, R8 (LSE)  | ON, OFF, OFF, O | LSE clock source is from external PC14 or PC14 and PC15 are used as GPIO. |  |  |

|-----------------------|-----------------|---------------------------------------------------------------------------|--|--|

|                       | ON              | VREF+ is connected to VDD                                                 |  |  |

| R17 (VREF+)           |                 | VREF+ is connected to the J2 pin_21 or of Arduino™                        |  |  |

| Titt/ (VIILI +)       | OFF             | connector J3 AREF                                                         |  |  |

| R19, R21              | ON, OFF         | User button B2 is connected to PA0                                        |  |  |

| (USER button B2)      | OFF, ON         | User button B2 is connected to PC13                                       |  |  |

|                       |                 | When PA11 and PA12 are used as USB, they are not                          |  |  |

|                       | OFF, OFF        | connected to pin_20 and pin_21 of J1.                                     |  |  |

| R29, R30 (PA11, PA12) |                 | When PA11 and PA12 are not used as USB, they can be                       |  |  |

|                       | ON, ON          | connected to pin_20 and pin_21 of J1.                                     |  |  |

|                       |                 | ArduinoTM A4 and A5 are connected to ADC_IN11 and                         |  |  |

|                       | OFF, ON, OFF, O | ADC_IN10                                                                  |  |  |

| R31, R32, R33, R34    |                 |                                                                           |  |  |

| (ArduinoTM A4, A5)    | ON OFF ON OF    | ArduinoTM A4 and A5 are connected to I2C1_SDA and                         |  |  |

|                       | ON, OFF, ON, OF | I2C1_SCL                                                                  |  |  |

| R35, R36              | OFF, ON         | ArduinoTM D10 is connected to SPI1_SS                                     |  |  |

| (ArduinoTM D10)       | ON, OFF         | ArduinoTM D10 is connected to PWM (TMR4_CH1)                              |  |  |

|                       |                 | USART1_RX of AT32F403AVGT7 is connected to VCP TX                         |  |  |

|                       | ON              | of AT-Link-EZ                                                             |  |  |

| R9 (USART1_RX)        |                 | USART1_RX of AT32F403AVGT7 is disconnected from                           |  |  |

|                       | OFF             | VCP TX of AT-Link-EZ                                                      |  |  |

|                       |                 | USART1_TX of AT32F403AVGT7 is connected to VCP RX                         |  |  |

|                       | ON              | of AT-Link-EZ                                                             |  |  |

| R10 (USART1_TX)       |                 | USART1_TX of AT32F403AVGT7 is disconnected from                           |  |  |

|                       | OFF             | VCP RX of AT-Link-EZ                                                      |  |  |

#### **Extension connectors**

ArduinoTM Uno R3 extension connector

Female plug J3~J6 and male J7 support standard ArduinoTM Uno R3 connectors. Most of the daughter boards designed around ArduinoTM Uno R3 are suitable for AT-START-F403A.

#### Note

- 1. The I/O ports of AT32F403AVGT7 are 3.3 V compatible with ArduinoTM Uno R3, but 5V incompatible.

- 2. Set R17 OFF if it is needed to supply power through the J3 pin\_8 AREF of AT-START-F403A to the VREF+ of AT32F403AVGT7 by means of ArduinoTM Uno R3 daughter board.

Table 4. ArduinoTM Uno R3 extension connector pin definition

|                               | Pin    | Arduino  | AT32F403A     |                         |

|-------------------------------|--------|----------|---------------|-------------------------|

| Connector                     | number | pin name | pin name      | Functions               |

|                               | 1      | NC       | _             | -                       |

|                               | 2      | IOREF    | -             | 3.3V reference          |

|                               | 3      | RESET    | NRST          | External reset          |

|                               | 4      | 3.3V     | -             | 3.3V input/output       |

|                               | 5      | 5V       | _             | 5V input/output         |

| J4                            | 6      | GND      | -             | Ground                  |

| (Power supply)                | 7      | GND      | -             | Ground                  |

|                               | 8      | VIN      | -             | 7~12V input/output      |

|                               | 1      | A0       | PA0           | ADC123_IN0              |

|                               | 2      | A1       | PA1           | ADC123_IN1              |

|                               | 3      | A2       | PA4           | ADC12_IN4               |

| J6                            | 4      | A3       | PB0           | ADC12_IN8               |

| (Analog input)                | 5      | A4       | PC1 or PB9(1) | ADC123_IN11 or I2C1_SDA |

| ,                             | 6      | A5       | PC0 or PB8(1) | ADC123_IN10 or I2C1_SCL |

|                               | 1      | D0       | PA3           | USART2_RX               |

|                               | 2      | D1       | PA2           | USART2_TX               |

|                               | 3      | D2       | PA10          | -                       |

|                               | 4      | D3       | PB3           | TMR2_CH2                |

| J5                            | 5      | D4       | PB5           | -                       |

| (Logic input/output low byte) | 6      | D5       | PB4           | TMR3_CH1                |

|                                 | 7  | D6    | PB10             | TMR2_CH3              |

|---------------------------------|----|-------|------------------|-----------------------|

|                                 | 8  | D7    | PA8(2)           | -                     |

|                                 | 1  | D8    | PA9              | -                     |

|                                 | 2  | D9    | PC7              | TMR3_CH2              |

|                                 | 3  | D10   | PA15 or PB6(1)(2 | SPI1_NSS or TMR4_CH1  |

|                                 | 4  | D11   | PA7              | TMR3_CH2 or SPI1_MOSI |

|                                 | 5  | D12   | PA6              | SPI1_MISO             |

|                                 | 6  | D13   | PA5              | SPI1_SCK              |

| J3                              |    |       |                  |                       |

| (Logic input/output high byte ) | 7  | GND   | _                | Ground                |

|                                 | 8  | AREF  | _                | VREF+ input/output    |

|                                 | 9  | SDA   | PB9              | I2C1_SDA              |

|                                 |    |       |                  |                       |

|                                 | 10 | SCL   | PB8              | I2C1_SCL              |

|                                 | 1  | MISO  | PB14             | SPI2_MISO             |

|                                 | 2  | 5V    | _                | 5V input/output       |

|                                 | 3  | SCK   | PB13             | SPI2_SCK              |

|                                 | 4  | MOSI  | PB15             | SPI2_MOSI             |

|                                 | 5  | RESET | NRST             | External reset        |

1.  $0 \Omega$  resistor setting is shown in Table 3.

6

7

8

2. SPIM must be disabled and JP8 one-piece jumper must select I/O side, otherwise PA8 and PB6 cannot be used.

PB12

PB11

**GND**

NSS

PB11

Ground

SPI2\_NSS

## LQFP100 I/O extension connector

The extension connector J1 and J2 can connect the AT-START-F403A to external prototype/packing board. The I/O ports of AT32F403AVGT7 are available on these extension connectors. J1 and J2 can also be measured with the oscilloscope, logic analyzer or voltmeter probe.

## Note

J7

(Others)

1. Set R17 OFF if it is necessary to supply power through the J2 pin\_21 VREF+ of AT-START-F403A with an external power supply,

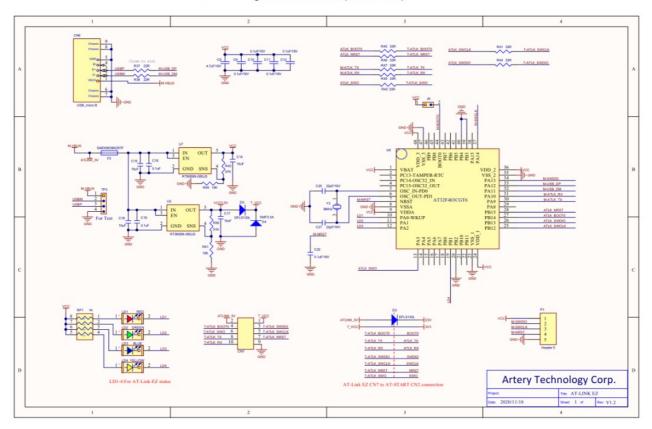

Figure 4. Schematic (AT-Link-EZ)

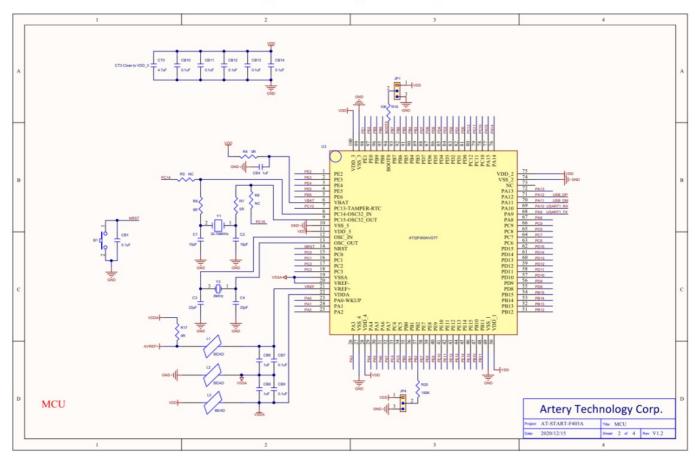

Figure 5. Schematic (microcontroller)

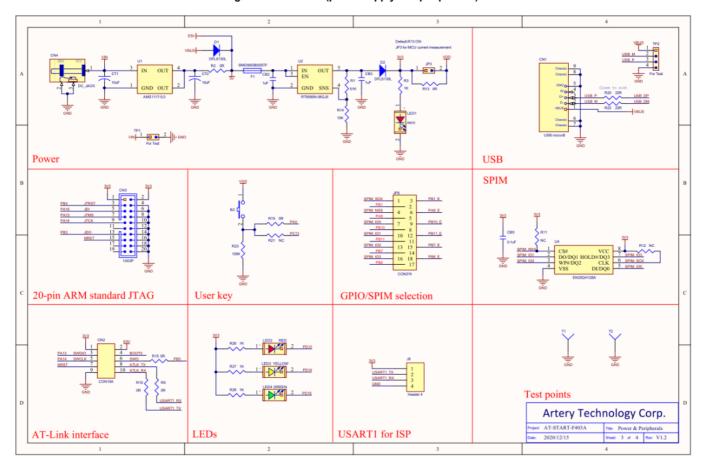

Figure 6. Schematic (power supply and peripherals)

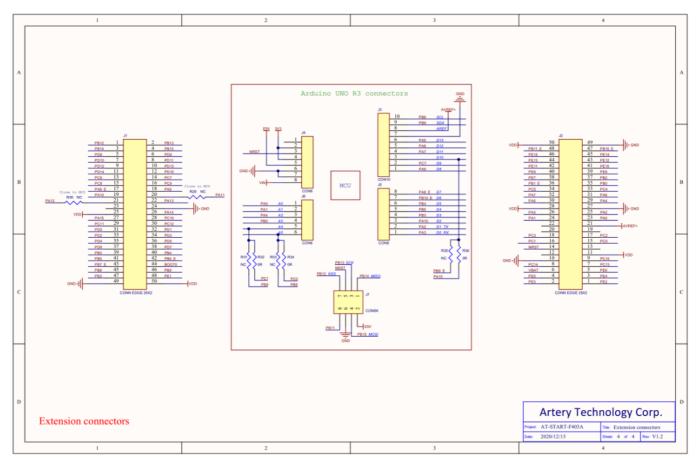

Figure 7. Schematic (extension connectors)

Table 5. Document revision history

| Date       | Revision | Changes                                                                                                                                                                                   |  |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2020.2.14  | 1.0      | Initial release                                                                                                                                                                           |  |

| 2020.4.22  | 1.1      | Modified LED3 to yellow                                                                                                                                                                   |  |

|            |          | Updated the revision code of this document to 3 digits, with the first two for AT-START version, and the last one for the document version.                                               |  |

|            |          | 2. Updated AT-Link-EZ hardware to V1.2. Support SWO debug, added the SWO description; and adjusted the CN7 signals, and corrected silkscreen in accordance with Artery development tools. |  |

|            |          | 3. Modified CN2 silkscreen.                                                                                                                                                               |  |

| 2020.12.15 | 1.20     | Added GND test ring to facilitate measurement.                                                                                                                                            |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

Purchasers understand and agree that purchasers are solely responsible for the selection and use of Artery's products and services.

Artery's products and services are provided "AS IS" and Artery provides no warranties express, implied or statutory, including, without limitation, any implied warranties of merchantability, satisfactory quality, non-infringement, or fitness for a particular purpose with respect to the Artery's products and services. Notwithstanding anything to the contrary, purchasers acquires no right, title or interest in any Artery's products and services or any intellectual property rights embodied therein. In no event shall Artery's products and services provided be construed as (a) granting purchasers, expressly or by implication, estoppel or otherwise, a license to use third party's products and services; or (b) licensing the third parties' intellectual property rights; or (c) warranting the third party's products and services and its intellectual property rights.

Purchasers hereby agrees that Artery's products are not authorized for use as, and purchasers shall not integrate, promote, sell or otherwise transfer any Artery's product to any customer or end user for use as critical components in (a) any medical, life saving or life support device or system, or (b) any safety device or system in any automotive application and mechanism (including but not limited to automotive brake or airbag systems), or (c) any nuclear facilities, or (d) any air traffic control device, application or system, or (e) any weapons device, application or system, or (f) any other device, application or system where it is reasonably foreseeable that failure of the Artery's products as used in such device, application or system would lead to death, bodily injury or catastrophic property damage.

© 2020 ARTERY Technology Corporation - All rights reserved

**Documents / Resources**

## ArteryTek AT32F403AVGT7 32 Bit Microcontrollers [pdf] User Manual

AT32F403AVGT7 32 Bit Microcontrollers, AT32F403AVGT7, 32 Bit Microcontrollers, Bit Microcontrollers, Microcontrollers

## References

- <u>■ :: 32 !</u> • <u>■ :: 32 !</u>

- User Manual

Manuals+, Privacy Policy