# **ANALOG DEVICES MAX98366 Evaluation System User Guide**

Home » Analog Devices » ANALOG DEVICES MAX98366 Evaluation System User Guide 🖺

#### **Contents**

- 1 ANALOG DEVICES MAX98366 Evaluation System User Guide

- **2 General Description**

- 3 Features

- **4 EV System Contents**

- **5 EV System Photo**

- 6 Quick Start

- 7 MAX98366 Evaluation System

- **8 Detailed Description of Hardware**

- 9 Table 1. Power Supplies

- 10 MAX98366 DEV Board Bill of Materials

- 11 MAX98366 DEV Board Schematic

- **12 Revision History**

- 13 Documents / Resources

- 13.1 References

# **ANALOG DEVICES MAX98366 Evaluation System User Guide**

The MAX98366 evaluation system (EV system) is a fully assembled and tested system that evaluates the MAX98366A/B/C/D mono Class-D audio amplifier with ultrasound support. The EV system consists of a MAX98366 Development Board (DEV board), an Audio Interface Board III (AUDINT3), and a USB cable.

It is recommended that the DEV board be evaluated with the AUDINT3 board, as an EV system. MAX98366A and MAX98366C support the standard I2S interface, and MAX98366B and MAX98366D support standard leftjustified mode. All MAX98366 variants support an 8- channel TDM digital audio interface.

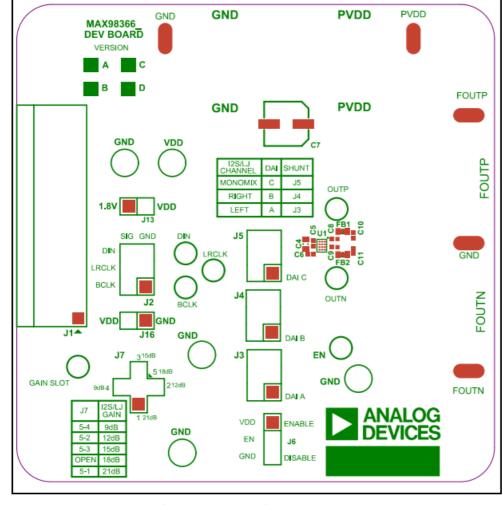

The AUDINT3 board provides a USB-to-PCM interface and a 1.8V VDD supply needed to evaluate the DEV board. The MAX98366 DEV board requires one additional supply input, 3V to 15V (PVDD) when evaluating using the AUDINT3 board. Figure 1 details the DEV board and the AUDINT3 board.

## **Features**

- Simple Plug-and-Play Design—No I2C Register Programming Required

- Wide Amplifier Supply Range (3V to 15V)

- Wideband Filters for Sample Rates ≥ 50kHz, Enabling Ultrasound Applications

- Sample Rates of 8kHz to 192kHz

- · I2S, Left-Justified, or TDM Input

- Five Selectable Gains (9.5dB, 12.5dB, 15.5dB, 18.5dB, and 21.5dB)

- Audio Channel Select (Left, Right, and Mono Mix)

- Filter Less Operation

- Low EMI

- Complete Hardware System with Easy Setup; No Tools or Special Software Required

#### **EV System Contents**

- MAX98366 Development Board

- Audio Interface Board III (AUDINT3)

- Micro-USB Cable

Ordering Information appears at end of data sheet.

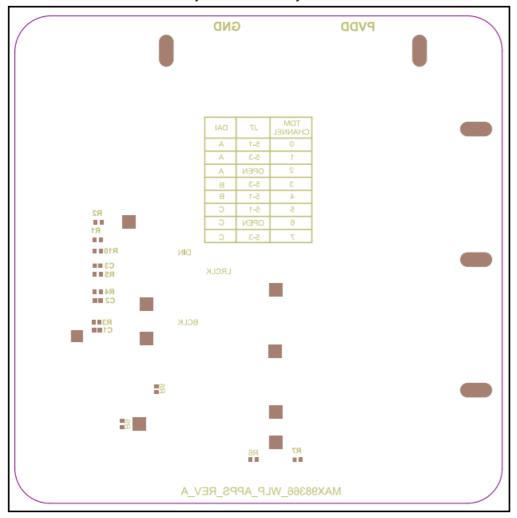

# **EV System Photo**

Figure 1. MAX98366 Evaluation System

#### **Quick Start**

**Note:** In the following sections, text in **bold and underlined** refers to items from the Windows operating system.

# **Required Equipment**

- MAX98366 EV System

- MAX98366 Development Board (DEV Board)

- Audio Interface Board III (AUDINT3 Board)

- Micro-USB Cable

- DC Power Supply (3V to 15V, 4A)

- 4Ω to 8Ω Speaker

- PC with Windows® 7 or Windows 10 with Available USB Port

- USB Audio Source (e.g., Spotify®, YouTube®, iTunes®)

## **Reference Material**

• MAX98366 IC data sheet

## Procedure

The MAX98366 and AUDINT3 boards are fully assembled and tested. Follow the steps below to set up the EV system for device evaluation.

# **AUDINT3 Board Setup:**

- Connect the MAX98366 DEV board (J1 connector) to the AUDINT3 board (J1 connector). It is important to

ensure the two boards' connectors are properly aligned to avoid damage. The bottom row of both J1

connectors should be lined up so the standoffs on the corners of the AUDINT3 and DEV board are level.

- 2. With the audio source disabled, connect the Micro-USB cable from your computer to the USB port (J2) on the AUDINT3 board. The AUDINT3 board provides the BCLK and LRCLK signals as well as the power for VDDIO, sourcing 1.8V to the DEV board through the J1 connector.

- 3. The multi-color LED D1 initially flashes blue, and then should change to slow flashing magenta when the computer successfully registers the AUDINT3 as a USB audio playback device.

#### **DEV Board Setup:**

- 1. Connect the AUDINT3 VDD jumper. Place one shunt on jumper J13 across pins labeled 1.8V and VDD. This allows the AUDINT3 to provide 1.8V to the VDD pin on MAX98366.

- 2. Configure the I2S channel jumper. Place a triple shunt on jumper J5, DAI C for mono-mix. Remove any shunts from J4, J3, and J2.

- 3. Set the GAIN\_SLOT jumper. Place one shunt on jumper J7 for desired gain (can use 21.5dB for PVDD = 15V).

- 4. Place the shunt on jumper J6 across pins VDD and EN.

- 5. Connect the speaker. Connect the speaker leads across the FOUTP and FOUTN binding posts.

- 6. Connect PVDD. With the DC supply not powered, connect the 3V to 15V power supply across the PVDD and GND binding posts.

#### **USB Audio Playback Test:**

- 1. Enable the PVDD supply voltage (3V to 15V, 4A).

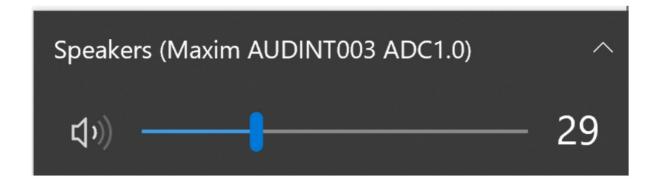

- 2. In the Window's **Sound Settings** set the "Maxim AUDINT003 ADC1.0" option as your output device, as seen in Figure 2.

- 3. Once done, the AUDINT3 board outputs PCM data to the DIN pin on the DEV board.

- 4. Adjust the audio source volume to a low level.

- 5. Enable the audio source and verify that audio is heard through the connected speaker. Adjust the audio source volume as needed.

#### MAX98366 Evaluation System

Figure 2. AUDINT3 as Playback Device

## **Detailed Description of Hardware**

The MAX98366 EV system is designed to thoroughly evaluate the MAX98366 digital input Class-D audio amplifier IC.

The EV system includes the MAX98366 Development Board (DEV board), the Audio Interface Board III (AUDINT3), and a micro-USB cable.

To simplify evaluation, the MAX98366 DEV board can be used together with the AUDINT3 and only one external power supply for PVDD. The AUDINT3 supplies 1.8V for VDD and a plug-and-play USB-to-I2S interface, allowing any computer to become a 48kHz digital audio source. The AUDINT3 board provides a fast and easy-to-use method for exercising the main capabilities of the device with no additional audio equipment.

The AUDINT3 board automatically senses the MAX98366 DEV board and configures its LDO regulators to power the MAX98366 DEV board's VDD pin through connector J1. The USB-to-PCM converter accepts a USB audio stream from a USB-connected computer and converts to I2S (MAX98366A/C) or left-justified (MAX98366B/D) data stream, allowing for USB audio playback through the MAX98366 device. The AUDINT3 board should not be used to deliver audio input when directly driving the DEV board's PCM interface with external audio test equipment. The digital audio interface (DAI) pins on the DEV board and AUDINT3 digital audio outputs are connected through the J1 header, creating a signal conflict.

For maximum flexibility, the MAX98366 DEV board can also be evaluated as a standalone board, with two external power supplies (PVDD and VDD), and the digital audio signal is driven directly by specialized audio test equipment (Audio Precision, etc.)

#### **Power Supplies**

When evaluated as a standalone board, the MAX98366 DEV board requires two external power supplies: PVDD, which is the supply voltage for the main Class-D power stage, and VDD, which supplies low-level system power to the IC. The voltage applied to VDD determines the logic level of the EN pin when J6 is in the ENABLE position. The power supplies and their ranges are listed in Table 1. The external supply voltages can be connected at the respective supply test points and/or binding posts.

**Table 1. Power Supplies**

| POWER SUPPLY | VOLTAGE RANGE (V) |

|--------------|-------------------|

| VDD          | 1.71 to 5.5       |

| PVDD         | 3 to 15           |

The AUDINT3 board, when properly connected to the DEV board, senses, and automatically provides 1.8V to VDD of MAX98366 DEV board through jumper J1, when active USB power is supplied. Note that with the AUDINT3 board connected, VDD is automatically provided, but an external PVDD is still required. If an external VDD is desired with AUDINT3 still connected to the DEV board, jumper J13 (DEV board) can be used to disconnect the AUDINT3's 1.8V. See *Table 2* for the J13 jumper selection.

Table 2. VDD Supply Selection Jumper J13

| J13 SHUNT POSITION | DESCRIPTION                                             |

|--------------------|---------------------------------------------------------|

| 1-2                | VDD supplied by AUDINT3 (through J1)                    |

| OPEN               | External power supply applied at VDD and GND test posts |

Jumper SelectionENABLE/DISABLE Selection (Shutdown Mode)The DEV board includes header J6 for device enable. The MAX98366 device features a low-power shutdown mode that is activated by setting the J6 shunt in the "DISABLE" position. To exit shutdown mode, place the J6 shunt in the "ENABLE" position. When the PCM

master is disabled and J6 is in the "ENABLE" position, the device is in standby mode. Enabling the PCM interface while J6 is in the "ENABLE" position puts the device in active playback mode, and the device output begins switching. See <u>Table 3</u> for reference.

Table 3. EN Selection Jumper J6

| J6 SHUNT POSITION | DESCRIPTION      |

|-------------------|------------------|

| EN to VDD         | Normal operation |

| EN to GND         | Shutdown         |

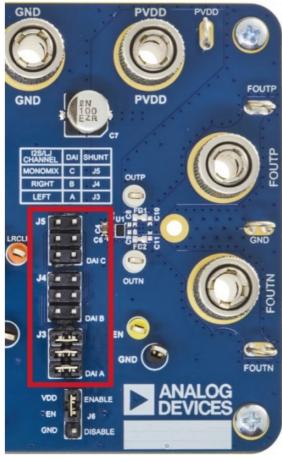

Gain and Channel Selection (I2S/Left-Justified Mode) The MAX98366's GAIN\_SLOT pin is connected to the center pin (pin 1) of the J7 header. When operating the device in I2S or left-justified mode, shunting pin 1 to the adjacent pins of the J7 header controls the PCM gain. *Table 4* shows the available gain settings in I2S and left-justified modes. In I2S and left-justified modes, channel selection is controlled by placing three shunts across the DAI configuration headers J3, J4, or J5. Each of the DAI configuration headers represents one valid mapping of the DAI pins to the PCM input signals. See *Table 5* for the valid jumper settings for the DAI configuration headers. Only one DAI configuration can be used at a time. *Figure 3* shows the shunt positions used for DAI configuration A.

Table 4. GAIN\_SLOT Selection Jumper J7

| GAIN (dB) | J7 SHUNT POSITION | GAIN_SLOT                                  |

|-----------|-------------------|--------------------------------------------|

| 21.5      | 1-5               | Connected to GND                           |

| 18.5      | Open              | Unconnected                                |

| 15.5      | 1-3               | Connected to VDD                           |

| 12.5      | 1-2               | Connected to VDD through 100kΩr esistor R1 |

| 9.5       | 1-4               | Connected to GND through 100kΩr esistor R1 |

Table 5. DAI Configuration Selection Jumper J3 to J5

| I2S/LJ CHANNEL              | JUMPER | DAI CONFIGURATION |

|-----------------------------|--------|-------------------|

| Left                        | J3     | А                 |

| Right                       | J4     | В                 |

| Mono-mix (Left/2 + Right/2) | J5     | С                 |

Figure 3. DAI Configuration A (Left-Channel for I2S/Left-Justified Operation)

# **Channel Selection (TDM Mode)**

In TDM mode, the MAX98366 has a fixed gain of 21.5dB and the GAIN\_SLOT pin becomes repurposed for TDM channel selection. The MAX98366 accepts 8-channel TDM data with either 16-bit or 32-bit data. The GAIN\_SLOT pin and DAI configuration are used to select which of the 8 channels of TDM data the part responds to, as shown in Table 6.

**Table 6. TDM Mode Channel Selection Jumper J4**

| TDM CHANNEL | J4 SHUNT POSITION | DAI CONFIGURATION |

|-------------|-------------------|-------------------|

| 0           | 1-5               | A                 |

| 1           | 1-3               | А                 |

| 2           | Open              | А                 |

| 3           | 1-3               | В                 |

| 4           | 1-5               | В                 |

| 5           | 1-5               | С                 |

| 6           | Open              | С                 |

| 7           | 1-3               | С                 |

### **DAI Header**

The DAI header J2 provides access to MAX98366's PCM bus (BCLK, LRCLK, and DIN). This DAI header facilitates evaluation with audio equipment I/O. See Table 7 for the pinout of the DAI header. Figure 4 shows a close-up image of the MAX98366 DAI interface header (J2) to be used if connecting external DAI inputs, such as those provided by Audio Precision or other audio test equipment.

Table 7. DAI Header J2

| SIGNAL | PIN | PIN | SIGNAL |

|--------|-----|-----|--------|

| DIN    | 6   | 5   | GND    |

| LRCLK  | 4   | 3   | GND    |

| BCLK   | 2   | 1   | GND    |

Figure 4. MAX98366 DAI Interface Headers (PCM)

#### **Speaker Output**

The MAX98366 audio output is routed to the FOUTP and FOUTN connections on the DEV board. The DEV board is, by default, assembled to allow the MAX98366 output to connect directly to a speaker load without the need for filtering.

#### **EMI Filter**

When long speaker cables are used with the MAX98366 output (exceeding ≈12in (30 cm)), a ferrite bead plus a capacitor filter can be installed to prevent excessive EMI radiation. Although it is best to choose filter components based on EMI test results, the combination of 100pF capacitors (C8, C9) and ferrite beads (L1, L2) generally works well. Before adding the filters to the design, first, remove the small PCB traces shorting the pads of L1 and L2 (see the MAX98366 DEV Board PCB Schematic and the MAX98366 DEV Board PCB Layout diagrams).

### **Audio Interface Board III**

The Audio Interface Board III (AUDINT3) facilitates the evaluation of the DEV board by providing a set of features that can be used to exercise the capabilities of the DEV board without the need for additional audio equipment. The main components of the AUDINT3 board are its LDO supply voltages and its USB-to-PCM interface. The supply voltages allow the DEV board to be evaluated with a minimal number of external supplies. The USB-to-PCM converter allows any computer to be used as an audio source for the DEV board's digital audio PCM

interface.

The MAX98366 DEV board connects to the AUDINT3 board through connector J1. The physical connections made between the DEV board and the AUDINT3 board are listed in <u>Table 8. Table 8. AUDINT3 Connector Table 8. AUDINT3 Connector J1</u>

| SIGNAL | PIN | SIGNAL | PIN | SIGNAL | PIN |

|--------|-----|--------|-----|--------|-----|

| _      | 1   | MCLK   | 2   | GND    | 3   |

| BCLK2  | 4   | BCLK1  | 5   | GPIO1  | 6   |

| LRCLK2 | 7   | LRCLK1 | 8   | GPIO2  | 9   |

| DAC2   | 10  | DAC1   | 11  | GPIO3  | 12  |

| ADC2   | 13  | ADC1   | 14  | GPIO4  | 15  |

| _      | 16  | ID     | 17  | 3.3V   | 18  |

| AVDD   | 19  | DVDD   | 20  | GND    | 21  |

| HPVD   | 22  | VDDIO  | 23  | GND    | 24  |

| GND    | 25  | SDA    | 26  | 5V     | 27  |

| _      | 28  | SCL    | 29  | 5V     | 30  |

| GND    | 31  | IRQ    | 32  | RST    | 33  |

| _      | 34  | _      | 35  | _      | 36  |

| GND    | 37  | _      | 38  | _      | 39  |

# **Ordering Information**

| PART            | TYPE                                                    |

|-----------------|---------------------------------------------------------|

| MAX98366AEVSYS# | I2S evaluation system with no volume ramping            |

| MAX98366BEVSYS# | Left-justified evaluation system with no volume ramping |

| MAX98366CEVSYS# | I2S evaluation system with volume ramping               |

| MAX98366DEVSYS# | Left-justified evaluation system with volume ramping    |

#Denotes RoHS-compliant.

# MAX98366 DEV Board Bill of Materials

| ITE<br>M | QT<br>Y | DESIGNAT<br>OR | MANUFACTURER P         | MANUFACTURE<br>R | VALUE | DESCRIPTION                            |

|----------|---------|----------------|------------------------|------------------|-------|----------------------------------------|

| 1        | 1       | C4             | GRM188R61E106MA<br>73D | Murata           | 10μF  | Cap / 10μF / 25V / 20% /<br>X5R / 0603 |

| 2  | 1 | C5                         | C1005X5R1V105K050<br>BC | TDK                     | 1μF               | Cap / 1µF / 35V / 10% / X<br>5R / 0402                             |

|----|---|----------------------------|-------------------------|-------------------------|-------------------|--------------------------------------------------------------------|

| 3  | 1 | C6                         | GRM155R61E105KA1<br>2D  | Murata                  | 1μF               | Cap / 1µF / 25V / 10% / X<br>5R / 0402                             |

| 4  | 1 | C7                         | EMZR250ARA101MF<br>61G  | United Chemi-Co         | 100μF             | Capacitor / Electrolytic / 1<br>00μF/ 25V / 20% / 6.3mm<br>x 6.1mm |

| 5  | 1 | J1                         | TSW-113-08-G-T-RA       | Samtec                  | 39 Pin He<br>ader | Updated EVkit Daughter<br>Card Header                              |

| 6  | 4 | J2, J3, J4, J<br>5         | TSW-103-07-G-D          | Samtec                  | 6 Pin<br>Header   | Header, 3×2 Position, 0.1 " Pitch                                  |

| 7  | 1 | J6                         | TSW-103-07-G-S          | Samtec                  | 3 Pin<br>Header   | Header, 3×1 Position, 0.1 " Pitch                                  |

| 8  | 1 | J7                         | TSW-105-07-F-S          | Samtec                  | 5 Pin<br>Header   | CONN HEADER VERT 5<br>POS 2.54MM                                   |

| 9  | 5 | J8, J9, J12,<br>J14, J15   | 20TCW                   | Weico Wire              | MAXIMPA<br>D      | Wire Loop / 20AWG / Tin<br>ned Copper / 25mm<br>Length             |

| 10 | 2 | J13, J16                   | TSW-102-07-G-S          | Samtec                  | 2 Pin<br>Header   | Header, 2×1 Position, 0.1 " Pitch                                  |

| 11 | 1 | R1                         | RC0402FR-0717K8L        | Yageo                   | 17.8k             | Resistor / 17.8kΩ / 1% / 1/16W/ 0402                               |

| 12 | 6 | R2, R3, R4,<br>R5, R7, R10 | RC0402FR-070RL          | Yageo                   | 0                 | Resistor / 0Ω / 1% / 1/16<br>W /0402                               |

| 13 | 2 | R8, R9                     | RC0402FR-07100KL        | Yageo                   | 100k              | Resistor / 100kΩ / 1% / 1<br>/16W/ 0402                            |

| 14 | 4 | SC1, SC2, S<br>C3, SC4     | 91772A106               | McMaster-Carr           | N/A               | Screw / 4-40 x 1/4" / Phill ips / Pan Head                         |

| 15 | 4 | ST1, ST2, S<br>T3, ST4     | 91780A164               | McMaster-Carr           | N/A               | Standoff / 4-40 x 1/2" / F<br>emale- Female / 1/4"<br>Hex          |

| 16 | 4 | TP1, TP6, T<br>P7, TP16    | 5011                    | Keystone<br>Electronics | N/A               | Test Point / Multi-<br>Purpose / Black                             |

| 17 | 3 | TP2, TP3, T<br>P4          | 5008                    | Keystone<br>Electronics | N/A               | Test Point / Compact / Or ange                                     |

| 18 | 2 | TP5, TP8                   | 5009                    | Keystone<br>Electronics | N/A               | Test Point / Compact / Ye llow                                     |

| 19       | 4       | TP9, TP10,<br>TP13, TP14    | 111-2223-001   | Johnson                 | N/A              | Binding Post                                   |

|----------|---------|-----------------------------|----------------|-------------------------|------------------|------------------------------------------------|

| 20       | 2       | TP11, TP12                  | 5007           | Keystone<br>Electronics | N/A              | Test Point / Compact / W hite                  |

| 21       | 1       | TP15                        | 5010           | Keystone<br>Electronics | N/A              | Test Point / Multi-<br>Purpose / Red           |

| 22       | 1       | U1                          | MAX98366AEWC+  | Analog Devices          | N/A              | 15V Plug-and-Play Class -D Amp with Ultrasound |

| DO N     | OT PI   | JRCHASE OR                  | POPULATE       |                         |                  |                                                |

|          |         |                             |                |                         |                  |                                                |

| ITE<br>M | QT<br>Y | DESIGNAT<br>OR              | MANUFACTURER P | MANUFACTURE<br>R        | VALUE            | DESCRIPTION                                    |

|          |         |                             | N              |                         | <b>VALUE</b> DNP | DESCRIPTION  Cap / Do Not Populate / 0402      |

| M        | Y       | OR C1, C2, C3, C8, C9, C10, | N              | R                       |                  | Cap / Do Not Populate /                        |

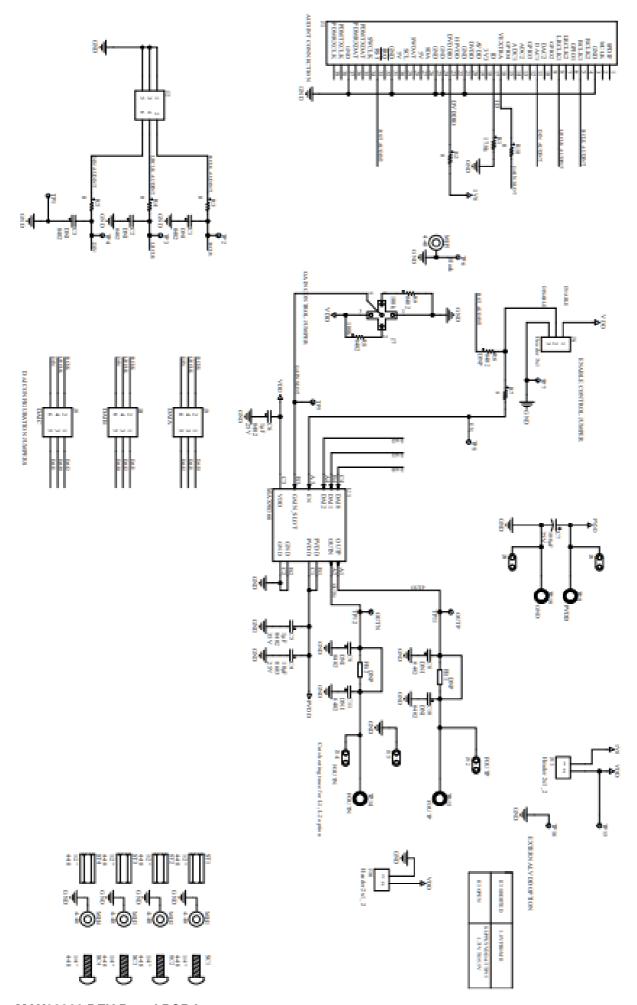

# **MAX98366 DEV Board Schematic**

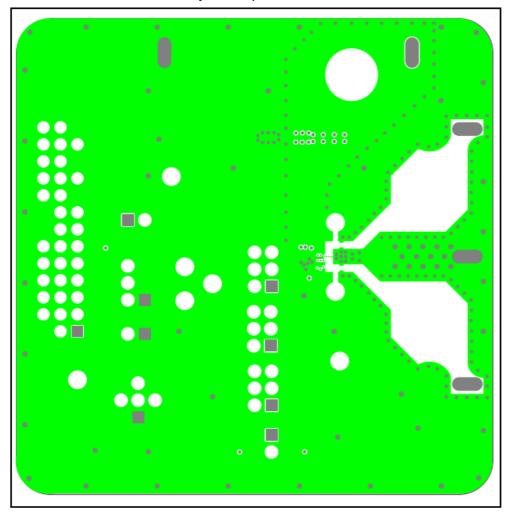

MAX98366 DEV Board PCB Layout—Top Silkscreen

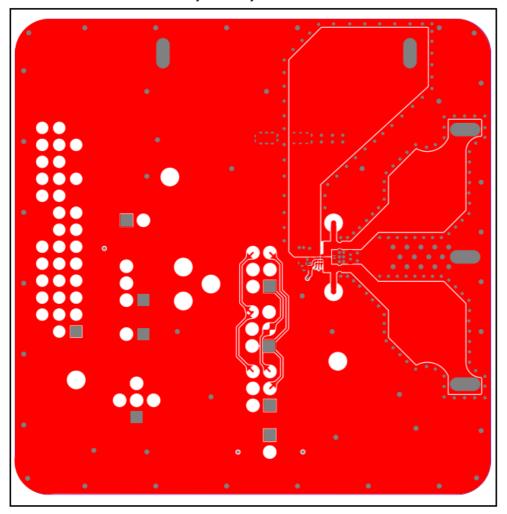

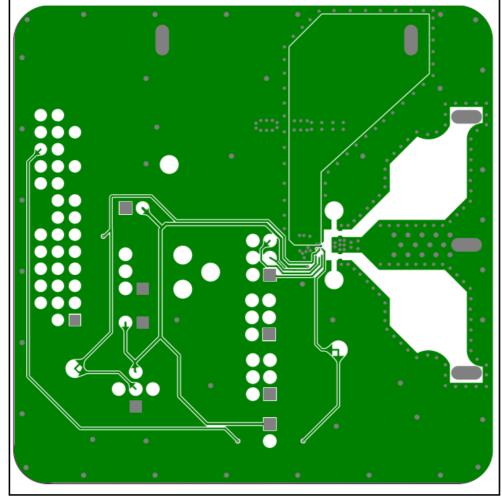

MAX98366 DEV Board PCB Layout—Layer 3

MAX98366 DEV Board PCB Layout—Layer 3

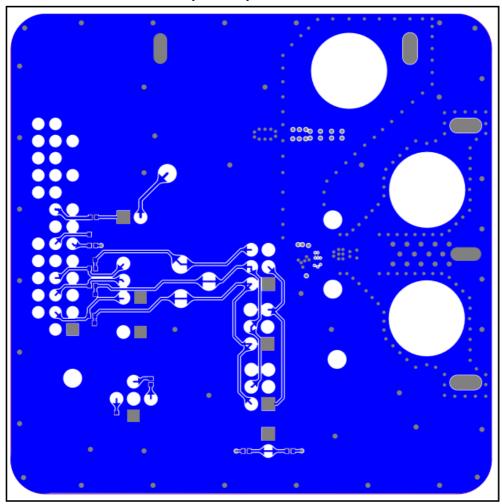

MAX98366 DEV Board PCB Layout—Bottom Silkscreen

## **Revision History**

| REVISIO<br>NNUMB<br>ER | REVISIO<br>NDATE | DESCRIPTION     | PAGESC<br>HANGED |

|------------------------|------------------|-----------------|------------------|

| 0                      | 3/24             | Initial release | _                |

ASSUMED BY ANALOG DEVICES FOR ITS USE, NOR FOR ANY INFRINGEMENTS OF PATENTS OR OTHER RIGHTS OF THIRD PARTIES THAT MAY RESULT FROM ITS USE. SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. NO LICENCE, EITHER EXPRESSED OR IMPLIED, IS GRANTED UNDER ANY ADI PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR ANY OTHER ADI INTELLECTUAL PROPERTY RIGHT RELATING TO ANY COMBINATION, MACHINE, OR PROCESS WHICH ADI PRODUCTS ALL INFORMATION CONTAINED HEREIN IS PROVIDED "AS IS" WITHOUT REPRESENTATION OR WARRANTY. NO RESPONSIBILITY IS OR SERVICES ARE USED. TRADEMARKS AND REGISTERED TRADEMARKS ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. analog.com

## **Documents / Resources**

ANALOG DEVICES MAX98366 Evaluation System [pdf] User Guide MAX98366, MAX98366 Evaluation System, Evaluation System, System

#### References

- Mixed-signal and digital signal processing ICs | Analog Devices

- O Document Feedback Form | Analog Devices

- Mixed-signal and digital signal processing ICs | Analog Devices

- User Manual

#### Manuals+, Privacy Policy

This website is an independent publication and is neither affiliated with nor endorsed by any of the trademark owners. The "Bluetooth®" word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. The "Wi-Fi®" word mark and logos are registered trademarks owned by the Wi-Fi Alliance. Any use of these marks on this website does not imply any affiliation with or endorsement.