# **ANALOG DEVICES EVAL-ADRF5700 5-Bit Silicon Digital Attenuator User Guide**

Home » Analog Devices » ANALOG DEVICES EVAL-ADRF5700 5-Bit Silicon Digital Attenuator User Guide 1

User Guide | EVAL-ADRF5700 UG-2152

Evaluating the ADRF5700, 2 dB LSB, 5-Bit, Silicon Digital Attenuator, 100 MHz to 22 GHz

# **Contents**

- 1 FEATURES

- **2 EVALUATION BOARD**

**HARDWARE**

**3 EVALUATION BOARD**

**HARDWARE**

- **4 TEST PROCEDURE**

- **5 ORDERING INFORMATION**

- 6 Documents / Resources

- **6.1 References**

# **FEATURES**

- Full featured evaluation board for the ADRF5700

- Simple connection to test equipment

- Through line for calibration

# **EQUIPMENT NEEDED**

- · DC power supplies

- · Network analyzer

#### **GENERAL DESCRIPTION**

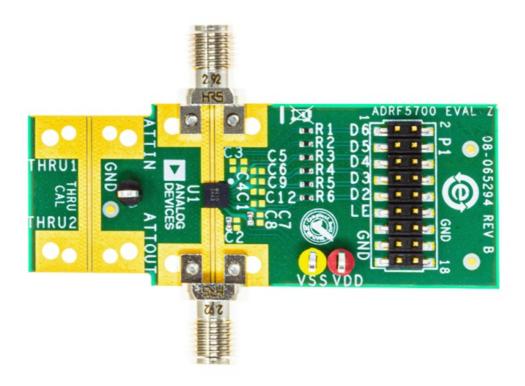

The ADRF5700 is a 100 MHz to 22 GHz, 2 dB LSB, 5-bit digital attenuator manufactured in the silicon process. This user guide describes the ADRF5700-EVALZ evaluation board, which was designed to simply evaluate the features and performance of the ADRF5700. A photograph of the evaluation board is shown in Figure 1. The ADRF5700 data sheet provides full specifications for the ADRF5700. Consult the ADRF5700 data sheet in conjunction with this user guide when using the ADRF5700-EVALZ.

### ADRF5700-EVALZ EVALUATION BOARD PHOTOGRAPH

Figure 1. Evaluation Board Photograph

### **EVALUATION BOARD HARDWARE**

# **OVERVIEW**

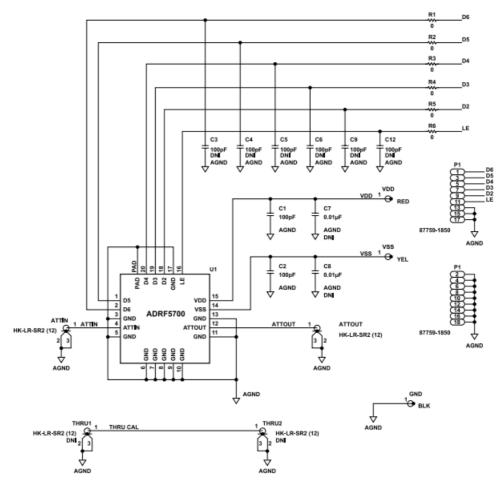

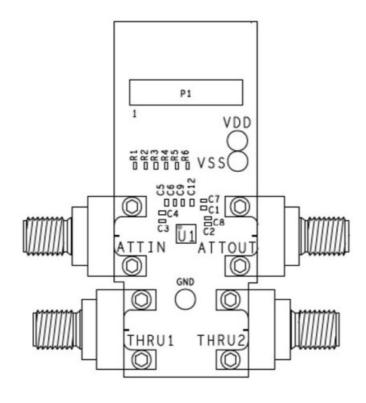

The ADRF5700-EVALZ is a connectorized board, assembled with the ADRF5700 and its application circuitry. All components are placed on the primary side of ADRF5700-EVALZ. An assembly drawing for the ADRF5700-EVALZ is shown in Figure 6 and an evaluation board schematic is shown in Figure 5.

### **BOARD LAYOUT**

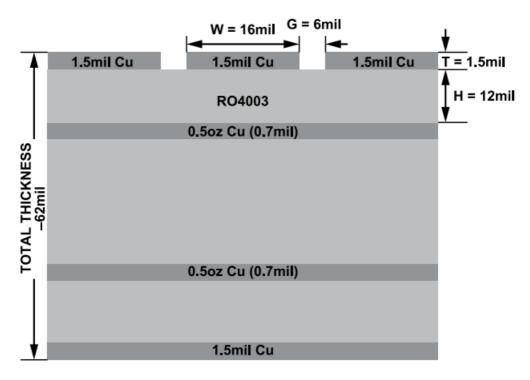

The ADRF5700-EVALZ was designed using RF circuit design techniques on a 4-layer printed circuit board (PCB). The PCB stack up is shown in Figure 2.

Figure 2. Evaluation Board Stack Up

The outer copper layers are 1.5 mil thick and the inner layers are 0.7 mil thick.

The top dielectric material is 12 mil Rogers 4003, which provides 50  $\Omega$  controlled impedance and optimizes the high-frequency performance. All RF traces are routed on the top layer, and the second layer is used as the ground plane for RF transmission lines.

The remaining two layers are also ground planes filled with FR4 material to manage the thermal rise during high-power operations and are supported with dense and filled vias to the PCB bottom for thermal relief. The overall board thickness is approximately 62 mil for mechanical strength.

The RF transmission lines are designed using a coplanar waveguide (CPWG) model with a width of 16 mil and ground spacing of 6 mil to have a characteristic impedance of 50  $\Omega$ . Ground via fences are arranged on both sides of a CPWG to improve isolation between nearby RF lines and other signal lines.

The exposed ground pad of the ADRF5700, which is soldered on the PCB ground pad, is the main thermal conduit for heat dissipation. The PCB ground pad is densely populated with filled, through vias to provide the lowest possible thermal resistance path from the top to the bottom of the PCB. The connections from the package ground leads to ground are kept as short as possible.

# POWER SUPPLY AND CONTROL INPUTS

The ADRF5700-EVALZ has two power supply inputs, six control inputs, and a ground, as shown in Table 1. The DC test points are populated on VDD, VSS, LE, D2, D3, D4, D5, D6, and GND.

A 3.3 V supply is connected to the DC test point on VDD and a -3.3 V supply is connected to the DC test point on VSS. Ground reference can be connected to GND. Connect the control inputs, LE, D2, D3, D4, D5, and D6 to 3.3 V or 0 V. The typical total current consumption for the ADRF5700 is 0.87 mA for control inputs = 0 V, and 0.67 mA for control inputs = 3.3 V.

The VDD and VSS supply pins of the ADRF5700 are decoupled with 100 pF capacitors.

# **Table 1. Power Supply and Control Inputs**

| Test Points | Description                                                |  |  |  |  |  |

|-------------|------------------------------------------------------------|--|--|--|--|--|

| VDD         | +3.3 V supply voltage                                      |  |  |  |  |  |

| VSS         | -3.3 V supply voltage                                      |  |  |  |  |  |

| LE          | Latch enable input                                         |  |  |  |  |  |

| D2          | Parallel control input for 2 dB attenuator bit             |  |  |  |  |  |

| D3          | Parallel control input for 4 dB attenuator bit             |  |  |  |  |  |

| D4          | Parallel control input for 8 dB attenuator bit             |  |  |  |  |  |

| D5          | Parallel control input for the first 16 dB attenuator bit  |  |  |  |  |  |

| D6          | Parallel control input for the second 16 dB attenuator bit |  |  |  |  |  |

| GND         | Ground                                                     |  |  |  |  |  |

### **RF INPUTS AND OUTPUTS**

The ADRF5700-EVALZ has four edge mounted, 2.92 mm connectors for the RF inputs and outputs, as shown in Table 2.

**Table 2. RF Inputs and Outputs**

| 2.92 mm Connectors | Description                   |

|--------------------|-------------------------------|

| ATTIN              | Attenuator input              |

| ATTOUT             | Attenuator output             |

| THRU1              | Through line input and output |

| THRU2              | Through line input and output |

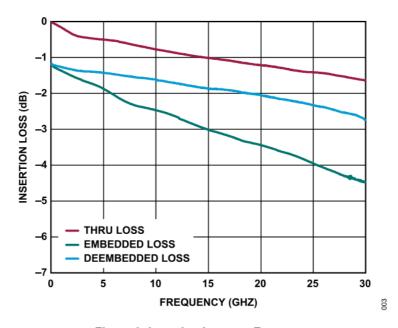

The through calibration line, connecting the THRU1 and THRU2 RF connectors, calibrates out the board loss effects from the measurements of the ADRF5700-EVALZ to determine the device performance at the pins of the IC. Figure 3 shows the typical board loss for the ADRF5700-EVALZ at room temperature, as well as the embedded and deembedded insertion loss for the ADRF5700.

# **EVALUATION BOARD HARDWARE**

Figure 3. Insertion Loss vs. Frequency

# **TEST PROCEDURE**

### **BIASING SEQUENCE**

To bias up the ADRF5700-EVALZ, perform the following steps:

- 1. Ground the GND test point.

- 2. Bias up the VDD test point.

- 3. Bias up the VSS test point

- 4. Bias up the LE, D2, D3, D4, D5, and D6 test points.

- 5. Apply an RF input signal.

The ADRF5700-EVALZ is shipped fully assembled and tested.

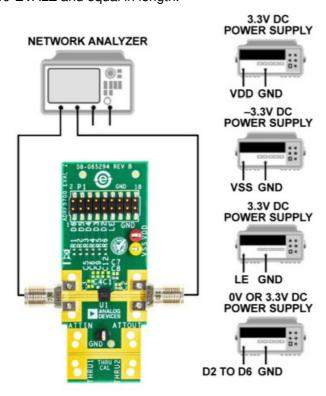

Figure 4 provides a basic test setup diagram to evaluate the S-parameters using a network analyzer. Perform the following steps to complete the test setup and to verify the operation of the ADRF5700-EVALZ in direct parallel mode:

- 1. Connect the GND test point to the ground terminal of the power supply.

- 2. Connect the VDD test point to the voltage output terminal of the +3.3 V supply.

- 3. Connect the VSS test point to the voltage output terminal of the -3.3 V supply.

- 4. Connect the LE, D2, D3, D4, D5, and D6 test points to the voltage output terminal of the 3.3 V supply. The ADRF5700 can be configured to have different attenuation levels by connecting the control test points to 3.3 V or 0 V, as shown in Table 3.

- 5. Connect a calibrated network analyzer to the ATTIN and ATTOUT 2.92 mm connectors. Sweep the frequency from 100 MHz to 22 GHz and set the power to –10 dBm.

Additional test equipment is needed to fully evaluate the ADRF5700-EVALZ functions and performance.

For third-order intercept point evaluation, use two signal generators and a spectrum analyzer. A high isolation power combiner is also recommended.

For power compression and power handling evaluations, use a 2channel power meter and a signal generator. A high enough power amplifier is also recommended at the input.

Test accessories, such as couplers and attenuators, must have enough power handling.

Note that the measurements performed at the 2.92 mm connectors of the ADRF5700-EVALZ include the losses of the 2.92 mm connectors and the PCB. The through line must be measured to calibrate out the effects on the ADRF5700- EVALZ. The through line is the summation of an RF input line and an RF output line that are connected to the ADRF5700-EVALZ and equal in length.

Figure 4. Test Setup Diagram

**Table 3. Truth Table**

| Digital Control Input1 |      |      |      |      |                        |  |  |

|------------------------|------|------|------|------|------------------------|--|--|

| D62                    | D52  | D4   | D3   | D2   | Attenuation State (dB) |  |  |

| Low                    | Low  | Low  | Low  | Low  | 0 (reference)          |  |  |

| Low                    | Low  | Low  | Low  | High | 2                      |  |  |

| Low                    | Low  | Low  | High | Low  | 4                      |  |  |

| Low                    | Low  | High | Low  | Low  | 8                      |  |  |

| Low                    | High | Low  | Low  | Low  | 16 (D5)                |  |  |

| High                   | Low  | Low  | Low  | Low  | 16 (D6)                |  |  |

| High                   | High | High | High | High | 46                     |  |  |

- 1. Any combination of the VCTRL input states provides an attenuation equal to the sum of the bits selected.

- 2. D5 and D6 both correspond to the 16 dB state. D5 has slightly better state accuracy at higher frequencies.

# **EVALUATION BOARD SCHEMATIC AND ARTWORK**

Figure 5. ADRF5700-EVALZ Evaluation Board Schematic

# **EVALUATION BOARD SCHEMATIC AND ARTWORK**

Figure 6. ADRF5700-EVALZ Evaluation Board Assembly Diagram

#### **BILL OF MATERIALS**

Table 4. Bill of Materials for the ADRF5700-EVALZ

| Quantity                        | Reference D esignator                                                          | Description                                                                                                                                                                                                                                                                                                | Manufacturer                                                                                                  | Part Number                                                                                                                            |

|---------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>6<br>2<br>2<br>2<br>1<br>1 | C1, C2 R1, R2, R3, R 4, R5, R6 ATTIN, ATTO UT THRU1, THR U2 VDD, VSS P1 U1 PCB | Capacitors, 100 pF, 50 V, C0 402 package Resistor, 0 Ω, 0402 package Edge mount 2.92 mm connec tors Edge mount 2.92 mm connec tors do not insert (DNI) Through hole, hold mount tes t points 18-pin male header, double r ow Silicon, 2 dB LSB, 5-bit digital attenuator, 100 MHz to 22 GHz ADRF5700-EVALZ | Murata Yageo Hirose Electric Hirose Electric Components Corporation Molex Analog Devices, Inc. Analog Devices | GCM1555C1H101JA16<br>D<br>RC0402JR-070RL<br>HK-LR-SR2(12)<br>HK-LR-SR2(12)<br>TP-104-01-00<br>87759-1850<br>ADRF5700BCCZN<br>BR-065294 |

# **ESD Caution**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **Legal Terms and Conditions**

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF

INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL.

ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2023 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. One Analog Way, Wilmington, MA 01887-2356, U.S.A.

### **Documents / Resources**

ANALOG DEVICES EVAL-ADRF5700 5-Bit Silicon Digital Attenuator [pdf] User Guide EVAL-ADRF5700, EVAL-ADRF5700 5-Bit Silicon Digital Attenuator, 5-Bit Silicon Digital Attenuator, Silicon Digital Attenuator, Digital Attenuator

### References

User Manual

Manuals+, Privacy Policy