## ams TMD3719 Flicker Detection User Guide

Home » ams » ams TMD3719 Flicker Detection User Guide 🖔

#### **Contents**

- 1 ams TMD3719 Flicker Detection

- 2 Introduction

- 2.1 FD\_CFG7 Register (Address 0x47)

- 2.2 ENABLE Register (Address 0x80)

- 3 CONTROL Register (Address 0xF6)

- **4 Flicker Detection Modes**

- **5 Documents / Resources**

- **5.1 References**

- **6 Related Posts**

ams TMD3719 Flicker Detection

#### Introduction

The TMD3719 features ambient light and color (RGB) sensing, proximity and flicker detection. The device integrates direct detection of ambient light flicker for 4 selectable frequency bins. There are two flicker detection modes; On-chip mode and data sampling mode. During the data sampling mode, the flicker detection engine can buffer data in a FIFO for calculating other flicker frequencies externally. In this document, the registers necessary to configure and the usage of both modes will be discussed.

## **Flicker Detection Registers**

The TMD3719 registers necessary to make the flicker function work are summarized in this section. These registers can also be found in the datasheet.

The values of all registers and fields that are listed as reserved or are not listed, must not be changed at any time.

## FD\_CFG0 Register (Address 0x40)

| Addr: | 0x40       | FD_CFG |      |                       |                 |

|-------|------------|--------|------|-----------------------|-----------------|

| Bit   | Field      | Reset  | Туре | Bit Description       |                 |

| 7:5   | Reserved   | 000    |      |                       |                 |

|       |            |        |      | Flicker Detection Nu  | mber of Samples |

|       |            |        |      | VALUE                 | SAMPLES         |

| 4.0   | ED CAMPLEO | 00     | R/W  | 0 (default)           | 128             |

| 4:3   | FD_SAMPLES |        |      | 1                     | 256             |

|       |            |        |      | 2                     | 512             |

|       |            |        |      | 3                     | 1024(1)         |

| 2     | Reserved   | 0      |      |                       |                 |

|       |            |        |      | Flicker Detection Tin | ne              |

| 4.0   | ED TIME    | 00     | DAM  | VALUE                 | TIME            |

| 1:0   | FD_TIME    | 00     | R/W  | 0                     | 50 ms           |

|       |            |        |      | 1 (default)           | 100 ms          |

|       |            |        |      |                       |                 |

| Addr | : 0x40   | FD_CFG | 0    |                 |                                                     |

|------|----------|--------|------|-----------------|-----------------------------------------------------|

| Bit  | Field    | Reset  | Туре | Bit Description |                                                     |

|      | <u> </u> | ·      |      | 2               | 200 ms                                              |

|      |          |        |      | 3               | User Defined by<br>FD_SAMPLE_TIME and<br>FD_SAMPLES |

## FD\_CFG0

1. If FD\_MODE = 1 (register 0x82 [6]) then the number of samples changes from 1024 to unlimited.

## FD\_CFG5 Register (Address 0x45)

| Addr: 0x45 |                       | FD_CFG5 |        |                                                                                                      |

|------------|-----------------------|---------|--------|------------------------------------------------------------------------------------------------------|

| Bit        | Bit Name              | Default | Access | Bit Description                                                                                      |

| 7:0        | FD_CHANNEL_DISABLE(1) | 0xFE    | R/W    | Flicker Detection Channel<br>Disable. Selects which<br>channels to be used for<br>flicker detection. |

## FD\_CFG5 Register

Select which modulator channels should be connected/used by the on\_ chip flicker engine. Note that the

bitstreams are added before the engine evaluates the data. The register bits are one hot encoded where bit 0

means modulator 0, and so on.

## FD\_CFG7 Register (Address 0x47)

| Addr: 0x47 |                  | FD_CFG7 |        |                                                                                                                                                      |

|------------|------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit        | Bit Name         | Default | Access | Bit Description                                                                                                                                      |

| 7:2        | Reserved         | 000000  |        |                                                                                                                                                      |

| 1:0        | FD_SAMPLE_TIME_H | 01      | R/W    | Flicker Detection Sample<br>Time High. These bits are<br>the high byte of the 10 bits<br>used for setting the flicker<br>detection integration time. |

## FD\_CFG7 Register

## FD\_CFG7 Register (Address 0x48)

| Addr: 0x48 |                  | FD_CFG8 | FD_CFG8 |                                                                                                                                                      |  |

|------------|------------------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name         | Default | Access  | Bit Description                                                                                                                                      |  |

| 7:2        | Reserved         | 000000  |         |                                                                                                                                                      |  |

| 1:0        | FD_SAMPLE_TIME_L | 01      | R/W     | Flicker Detection Sample<br>Time Low. This register is<br>the low byte of the 10 bits<br>used for setting the flicker<br>detection integration time. |  |

## FD\_CFG8 Register

## **ENABLE Register (Address 0x80)**

| Addr: 0x80 |          | ENABLE  |        |                                                                                                                                                                                                                                                               |

|------------|----------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit        | Bit Name | Default | Access | Bit Description                                                                                                                                                                                                                                               |

| 7          | Reserved | 0       |        |                                                                                                                                                                                                                                                               |

| 6          | FDEN     | 0       | R/W    | Flicker Detection Enable. Writing a 1 activates flicker detection. Writing a 0 disables flicker detection.                                                                                                                                                    |

| 5          | Reserved | 0       |        |                                                                                                                                                                                                                                                               |

| 4          | AEN      | 0       | R/W    | <b>ALS Enable</b> . Writing a 1 enables ALS/Color. Writing a 0 disables ALS/Color.                                                                                                                                                                            |

| 3          | PEN      | 0       | R/W    | <b>Proximity Enable.</b> Writing a 1 enables proximity. Writing a 0 disables proximity.                                                                                                                                                                       |

| 2:1        | Reserved | 00      |        |                                                                                                                                                                                                                                                               |

| 0          | PON      | 0       | R/W    | <b>Power ON.</b> When asserted, the internal oscillator is activated, allowing timers and ADC channels to operate. Writing a 0 disables the oscillator and clears PEN and AEN. Only set this bit after all other registers have been initialized by the host. |

ENABLE Registe

MEAS\_MODE1 Register (Address 0x82)

| Addr: | 0x82      | MEAS_MC | DDE1   |                                                                                   |                                       |

|-------|-----------|---------|--------|-----------------------------------------------------------------------------------|---------------------------------------|

| Bit   | Bit Name  | Default | Access | Bit Description                                                                   | n                                     |

| 7     | Reserved  | 0       |        |                                                                                   |                                       |

| 6     | FD_MODE   | 0       | R/W    | Flicker Detecti<br>Writing a 0 will<br>chip mode and<br>set the FD to da<br>mode. | set the FD to on-<br>writing a 1 will |

| 5:3   | Reserved  | 000     | R/W    |                                                                                   |                                       |

|       |           |         | 544    | FIFO Mode                                                                         |                                       |

|       |           |         |        | VALUE                                                                             | MODE                                  |

|       |           |         |        | 0                                                                                 | Off                                   |

| 0.0   | FIFO MODE | 0       |        | 1                                                                                 | 32-bit                                |

| 2:0   | FIFO_MODE | 0       | R/W    | 2                                                                                 | 16-bit ALS                            |

|       |           |         |        | 3                                                                                 | 16-bit FD                             |

|       |           |         |        | 4                                                                                 | 8-bit FD                              |

|       |           |         |        | 5 – 7                                                                             | Reserved                              |

## MEAS\_MODE1 Register MOD\_GAIN\_0\_1 Register (Address 0x89)

| Addr: | 0x89      | MOD_GAIN | MOD_GAIN_0_1 |                 |            |  |  |

|-------|-----------|----------|--------------|-----------------|------------|--|--|

| Bit   | Bit Name  | Default  | Access       | Bit Description | on .       |  |  |

|       |           |          |              | Modulator One   | e Gain     |  |  |

|       |           |          |              | VALUE           | GAIN       |  |  |

|       |           |          |              | 0               | 2x         |  |  |

|       |           |          |              | 1               | <b>4</b> x |  |  |

|       |           |          |              | 2               | 8x         |  |  |

|       |           |          |              | 3               | 16x        |  |  |

|       |           |          |              | 4               | 32x        |  |  |

| 7:4   | MOD_GAIN1 | 0000     | R/W          | 5               | 64x        |  |  |

|       |           |          |              | 6               | 128x       |  |  |

|       |           |          |              | 7               | 256x       |  |  |

|       |           |          |              | 8               | 512x       |  |  |

|       |           |          |              | 9               | 1024x      |  |  |

|       |           |          |              | 10              | 2048x      |  |  |

|       |           |          |              | 11              | 4096x      |  |  |

|       |           |          |              | 12 – 15         | Reserved   |  |  |

|       |           |          |              | Modulator Zer   | o Gain     |  |  |

|       |           |          |              | VALUE           | GAIN       |  |  |

|       |           |          |              | 0               | 2x         |  |  |

|       |           |          |              | 1               | 4x         |  |  |

|       |           |          |              | 2               | 8x         |  |  |

|       |           |          |              | 3               | 16x        |  |  |

|       |           |          |              | 4               | 32x        |  |  |

| 3:0   | MOD_GAIN0 | 0000     | R/W          | 5               | 64x        |  |  |

|       |           |          |              | 6               | 128x       |  |  |

|       |           |          |              | 7               | 256x       |  |  |

|       |           |          |              | 8               | 512x       |  |  |

|       |           |          |              | 9               | 1024x      |  |  |

|       |           |          |              | 10              | 2048x      |  |  |

|       |           |          |              | 11              | 4096x      |  |  |

|       |           |          |              | 12 – 15         | Reserved   |  |  |

| A al alas  | 004       | MOD_GAIN_2_3 |        |                 |            |  |

|------------|-----------|--------------|--------|-----------------|------------|--|

| Addr: 0x8A |           | MOD_GAIN     | _2_3   |                 |            |  |

| Bit        | Bit Name  | Default      | Access | Bit Description | on         |  |

|            |           |              |        | Modulator Thr   | ee Gain    |  |

|            |           |              |        | VALUE           | GAIN       |  |

|            |           |              |        | 0               | <b>2</b> x |  |

|            |           |              |        | 1               | <b>4</b> x |  |

|            |           |              |        | 2               | 8x         |  |

|            |           |              |        | 3               | 16x        |  |

|            |           |              |        | 4               | 32x        |  |

| 7:4        | MOD_GAIN3 | 0000         | R/W    | 5               | 64x        |  |

|            |           |              |        | 6               | 128x       |  |

|            |           |              |        | 7               | 256x       |  |

|            |           |              |        | 8               | 512x       |  |

|            |           |              |        | 9               | 1024x      |  |

|            |           |              |        | 10              | 2048x      |  |

|            |           |              |        | 11              | 4096x      |  |

|            |           |              |        | 12 – 15         | Reserved   |  |

|            |           |              |        | Modulator Two   | Gain       |  |

|            |           |              |        | VALUE           | GAIN       |  |

|            |           |              |        | 0               | 2x         |  |

|            |           |              |        | 1               | 4x         |  |

|            |           |              |        | 2               | 8x         |  |

|            |           |              |        | 3               | 16x        |  |

|            |           |              |        | 4               | 32x        |  |

| 3:0        | MOD_GAIN2 | 0000         | R/W    | 5               | 64x        |  |

|            |           |              |        | 6               | 128x       |  |

|            |           |              |        | 7               | 256x       |  |

|            |           |              |        | 8               | 512x       |  |

|            |           |              |        | 9               | 1024x      |  |

|            |           |              |        | 10              | 2048x      |  |

|            |           |              |        | 11              | 4096x      |  |

|            |           |              |        | 12 – 15         | Reserved   |  |

MOD\_GAIN\_2\_3 Register MOD\_GAIN\_4\_5 Register (Address 0x8B)

| Addr: | 0x8B      | MOD_GAIN | MOD_GAIN_4_5 |                 |            |  |  |

|-------|-----------|----------|--------------|-----------------|------------|--|--|

| Bit   | Bit Name  | Default  | Access       | Bit Description | on         |  |  |

|       |           |          |              | Modulator Five  | e Gain     |  |  |

|       |           |          |              | VALUE           | GAIN       |  |  |

|       |           |          |              | 0               | 2x         |  |  |

|       |           |          |              | 1               | 4x         |  |  |

|       |           |          |              | 2               | 8x         |  |  |

|       |           |          |              | 3               | 16x        |  |  |

|       |           |          |              | 4               | 32x        |  |  |

| 7:4   | MOD_GAIN5 | 0000     | R/W          | 5               | 64x        |  |  |

|       |           |          |              | 6               | 128x       |  |  |

|       |           |          |              | 7               | 256x       |  |  |

|       |           |          |              | 8               | 512x       |  |  |

|       |           |          |              | 9               | 1024x      |  |  |

|       |           |          |              | 10              | 2048x      |  |  |

|       |           |          |              | 11              | 4096x      |  |  |

|       |           |          |              | 12 – 15         | Reserved   |  |  |

|       |           |          |              | Modulator Fou   | ır Gain    |  |  |

|       |           |          |              | VALUE           | GAIN       |  |  |

|       |           |          |              | 0               | 2x         |  |  |

|       |           |          |              | 1               | <b>4</b> x |  |  |

|       |           |          |              | 2               | 8x         |  |  |

|       |           |          |              | 3               | 16x        |  |  |

|       |           |          |              | 4               | 32x        |  |  |

| 3:0   | MOD_GAIN4 | 0000     | R/W          | 5               | 64x        |  |  |

|       |           |          |              | 6               | 128x       |  |  |

|       |           |          |              | 7               | 256x       |  |  |

|       |           |          |              | 8               | 512x       |  |  |

|       |           |          |              | 9               | 1024x      |  |  |

|       |           |          |              | 10              | 2048x      |  |  |

|       |           |          |              | 11              | 4096x      |  |  |

|       |           |          |              | 12 – 15         | Reserved   |  |  |

MOD\_GAIN\_4\_5 Register MOD\_GAIN\_6\_7 Register (Address 0x8C)

| Addr: 0x8C |           | MOD_GAIN_ | MOD_GAIN_6_7 |                 |            |  |

|------------|-----------|-----------|--------------|-----------------|------------|--|

| Bit        | Bit Name  | Default   | Access       | Bit Description | n          |  |

|            |           |           |              | Modulator Sev   | en Gain    |  |

|            |           |           |              | VALUE           | GAIN       |  |

|            |           |           |              | 0               | 2x         |  |

|            |           |           |              | 1               | <b>4</b> x |  |

|            |           |           |              | 2               | 8x         |  |

|            |           |           |              | 3               | 16x        |  |

|            |           |           |              | 4               | 32x        |  |

| 7:4        | MOD_GAIN7 | 0000      | R/W          | 5               | 64x        |  |

|            |           |           |              | 6               | 128x       |  |

|            |           |           |              | 7               | 256x       |  |

|            |           |           |              | 8               | 512x       |  |

|            |           |           |              | 9               | 1024x      |  |

|            |           |           |              | 10              | 2048x      |  |

|            |           |           |              | 11              | 4096x      |  |

|            |           |           |              | 12 – 15         | Reserved   |  |

|            |           |           |              | Modulator Six   | Gain       |  |

|            |           |           |              | VALUE           | GAIN       |  |

|            |           |           |              | 0               | 2x         |  |

|            |           |           |              | 1               | 4x         |  |

|            |           |           |              | 2               | 8x         |  |

|            |           |           |              | 3               | 16x        |  |

|            |           |           |              | 4               | 32x        |  |

| 3:0        | MOD_GAIN6 | 0000      | R/W          | 5               | 64x        |  |

|            |           |           |              | 6               | 128x       |  |

|            |           |           |              | 7               | 256x       |  |

|            |           |           |              | 8               | 512x       |  |

|            |           |           |              | 9               | 1024x      |  |

|            |           |           |              | 10              | 2048x      |  |

|            |           |           |              | 11              | 4096x      |  |

|            |           |           |              | 12 – 15         | Reserved   |  |

MOD\_GAIN\_6\_7 Register

## CONTROL Register (Address 0xF6)

| Addr: 0xF6 |                  | CONTRO  | L      |                                                                                                                                 |

|------------|------------------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| Bit        | Bit Name         | Default | Access | Bit Description                                                                                                                 |

| 7:3        | Reserved         | 00000   |        |                                                                                                                                 |

| 2          | ALS_MANUAL_AZ    | 0       | R/W    | ALS Manual Autozero. Starts a manual autozero of the ALS engines. Set AEN = 0 before starting a manual autozero for it to work. |

| 1          | FIFO_CLR         | 0       | R/W    | FIFO Buffer Clear. Clears all FIFO data, FINT, FIFO_OV, and FIFO_LVL.                                                           |

| 0          | CLEAR_SAI_ACTIVE | 0       | R/W    | Clear Sleep-After-Interrupt Active.<br>Clears SAI_ACTIVE, ends sleep, and<br>restarts device operation.                         |

CONTROL Register FIFO\_MAP2 Register (Address 0xFA

| Addr: 0xFA |                       | FIFO_MAP2 |        |                                                                                                                               |  |

|------------|-----------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name              | Default   | Access | Bit Description                                                                                                               |  |

| 7:5        | Reserved              | 000       |        |                                                                                                                               |  |

| 4          | FIFO_WRITE_FD_RESULTS | 0         | R/W    | FIFO Write Flicker Detection Result. If asserted, flicker detection on-chip calculation result is written to the FIFO buffer. |  |

| 3          | FIFO_WRITE_FD_DATA    | 0         | R/W    | FIFO Write Flicker Detection Data. If asserted, flicker detection data is written to the FIFO buffer.                         |  |

| 2          | FIFO_WRITE_PDATAR     | 0         | R/W    | FIFO Write Proximity Ratio Data. If asserted, proximity ratio data is written to the FIFO buffer.                             |  |

| 1          | FIFO_WRITE_PDATA1     | 0         | R/W    | FIFO Write Proximity One Data. If asserted, proximity one data is written to the FIFO buffer.                                 |  |

| 0          | FIFO_WRITE_PDATA0     | 0         | R/W    | FIFO Write Proximity Zero Data. If asserted, proximity zero data is written to the FIFO buffer.                               |  |

# FIFO\_MAP2 Register FIFO STATUS Register (Address 0xFB)

| Add | r: 0xFB  | FIFO_STATUS |        |                                                                                                                                                                                |  |

|-----|----------|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit | Bit Name | Default     | Access | Bit Description                                                                                                                                                                |  |

| 7   | FIFO_OV  | 0           | R      | FIFO Buffer Overflow. Indicates that<br>the FIFO buffer overflowed and<br>information has been lost. Bit is<br>automatically cleared when the FIFO<br>is read.                 |  |

| 6:0 | FIFO_LVL | 0000000     | R      | FIFO Buffer Level. Indicates the number of entries (each are 4 bytes) available in the FIFO buffer waiting for readout. The FIFO level can be between 0 (empty) and 64 (full). |  |

# FIFO\_STATUS Register FIFO Buffer Data Register (Address 0xFC – 0xFF)

| Addr | Name         | Туре             | Description      | 7       | 6 | 5 | 4    | 3    | 2 | 1    | 0 | Reset |

|------|--------------|------------------|------------------|---------|---|---|------|------|---|------|---|-------|

| 0xFC |              |                  |                  |         |   |   | 0000 | 0000 |   |      |   | 0x00  |

| 0xFD | 0xFD FDATA R | Б                | FIFO buffer data |         |   |   |      | 0000 |   |      |   | 0x00  |

| 0xFE |              | FIFO bullet data |                  | 0000000 |   |   |      |      |   | 0x00 |   |       |

| 0xFF | _            |                  |                  |         |   |   | 0000 | 0000 |   |      |   | 0x00  |

#### **FIFO Buffer Data Register**

#### **Flicker Detection Modes**

#### **On-Chip Mode**

Flicker function can be activated by the flicker enable bit in register 0x80 bit 6 (MEAS\_MODE1.FDEN). Writing a 1 activates flicker detection. Writing a 0 disables flicker detection. The time to measure for flicker is set by using register FD\_CFG0.FD\_TIME (0x40 bits [1:0]). The sampling time can be set to 50/100/200 milliseconds for a frequency bin resolution of 20/10/5 Hz, respectively. Also, a user defined FD\_TIME can be defined by FD\_SAMPLE\_TIME in registers FD\_CFG7 (0x47 bits [7:0]) and FD\_CFG8 (0x48 [1:0]) in combination with FD\_SAMPLES of register FD\_CFG0 (0x40 bits [4:3]). When setting register FD\_CFG0.FD\_TIME (0x40 bits [1:0]) to one of the preset sampling times, registers FD\_CFG7 (0x47) and FD\_CFG8 (0x48) are set with a preset value for sample time. These preset values are shown in .

| Value | FD_TIME <sup>(3)</sup><br>0x40 bits [1:0] | FD_SAMPLES<br>0x40 bits [4:3] | FD_SAMPLE_TIME<br>0x47 & 0x48 |

|-------|-------------------------------------------|-------------------------------|-------------------------------|

| 0     | 50 ms <sup>(1)</sup>                      | 128                           | 143                           |

| 1     | 100 ms <sup>(1)</sup>                     | 128                           | 287                           |

| 2     | 200 ms <sup>(1)</sup>                     | 128                           | 575                           |

| 3     | User defined                              | 1024 <sup>(2)</sup>           | User Defined                  |

Registers FD CFG7 (0x47) and FD CFG8 (0x48) combine to make a 10-bit value.

#### Flicker Sampling Time Configurations

- 1. When selecting 50 ms/100 ms/200 ms, register FD\_SAMPLES gets overwritten with 128.

- 2. Unlimited, if FD\_MODE = 1, FIFO\_WRITE\_FD\_DATA = 1, and FIFO\_MODE > 0 else 1024.

- 3. FD\_TIME = FD\_SAMPLES \* (FD\_SAMPLE\_TIME + 1) \* modclk; modclk =  $2.71 \mu s$ .

For example:  $FD\_CFG0$  (0x40) = 0x01(default) – This selects  $FD\_TIME$  as 100 ms. Therefore,  $FD\_SAMPLES$  = 128 and  $FD\_SAMPLE\_TIME$  = 287.

The on-chip flicker function uses the Goertzel Algorithm embedded in the device.

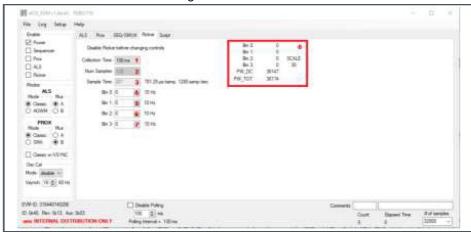

#### **TMD3719 GUI**

| Index | Description                                             | Register(s) [bits]                            | Comments                                                                                                                                     |

|-------|---------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Time to measure flicker                                 | 0x40 [1:0]                                    | 200 ms,<br>100 ms (Default),<br>50 ms,<br>user defined <sup>(1)</sup>                                                                        |

| 2     | Number of samples to be measured for flicker            | 0x40 [4:3]                                    | 128 (Default),<br>256,<br>512,<br>1024 (Unlimited <sup>(2)</sup> )                                                                           |

| 3     | Integration time for flicker                            | 0x47 [1:0], 0x48 [7:0]                        | Must not be changed with FDEN = 1 and PON = 1                                                                                                |

| 4-7   | Coefficients input to algorithm to decode bin distances | 0x41[4:0], 0x42[4:0],<br>0x43[4:0], 0x44[4:0] | Inputs to the on-chip algorithm. 200 ms: 5 Hz to 160 Hz, 5 Hz steps 100 ms: 10 Hz to 320 Hz, 10 Hz steps 50 ms: 20 Hz to 640 Hz, 20 Hz steps |

| 8     | Results from the algorithm                              |                                               |                                                                                                                                              |

### **Explanation of Fields in the Above GUI Image**

- 1. Can be used to select different combinations using number of samples (0x40 [4:3]) and sample time (0x47, 0x48).

- 2. If fd\_mode = 1, fifo\_write\_fd\_data = 1, and fifo\_ mode > 0 else 1024.

## **Data Sampling Mode**

This section gives guidance on configuring flicker for 16-bit sampling mode and accessing flicker detection data from the FIFO. This section shows an example of a specific flicker configuration. Adjustment to the configuration could be made for a different application. FIFO access can be read out with single reads starting at FDATA0 (0xFC). 4 consecutive I2C addresses have to be read to get a full data set. Upon reading FDATA3 (0xFF), then reading FDATA0 again (I2C address wrap around) it automatically decreases the FIFO\_STATUS.FIFO\_LVL (0xFB). If reading beyond the end of the FIFO, data will return 0x00. There is no under-run flag, this is not as error condition.

## **Configuring Flicker Detection:**

- 1. Configure ENABLE (0x80) = 0x01 (Enable PON).

- 2. Configure FD CFG0 (0x40) = 0x02 (FD TIME = 200 ms, FD SAMPLES = 128).

- 3. Configure MOD\_GAIN

- MOD GAIN 0 1 (0x89) = 0x02 (8x)

- MOD GAIN 2 3 (0x8A) = 0x02 (8x)

- $MOD\_GAIN\_4\_5 (0x8B) = 0x02 (8x)$

- MOD GAIN 6 7 (0x8C) = 0x02 (8x)

- 4. Configure FD CFG5 (0x45) = 0x00 (All flicker channels active).

- 5. Configure MEAS MODE1 (0x82) = 0x43 (FD MODE = sampling mode, FIFO MODE = 16 bits).

- 6. Configure FIFO MAP2 (0xFA) = 0x08 (Write data to FIFO).

#### Clearing the FIFO:

- 1. Read ENABLE register (0x80) contents and save it to a variable 'A'.

- 2. Set ENABLE register (0x80) to 0x1, only PON is enabled.

- 3. Read CONTROL register (0xF6) and save it to a variable 'B'.

- 4. Set variable 'B' bit 1 (FIFO\_CLR) to 1, leave other bits same.

- 5. Write 'B' back to CONTROL register (0xF6).

- 6. Write variable 'A' to ENABLE register (0x80) to recover the original state.

- 7. Configure ENABLE (0x80) = 0x41 (PON = 1, FDEN=1).

#### **Polling Flicker Data**

- 1. Read FIFO STATUS (0xFB).

- 2. Check FIFO\_OV (0xFB [7]) FIFO buffer overflow, if flag is set information has been lost.

- 3. Check FIFO LVL (0xFB [6:0]) FIFO level, indicates number of entries available.

- 4. If FIFO OV = 1 then;

- 5. Clear FIFO.

- 6. Delay 50 ms.

- 7. If FIFO LVL is not 0 then;

- 8. Poll FIFO buffer data FDATA (0xFC, 0xFD, 0xFE, 0xFF).

Polling of the FIFO should be done such that the FIFO does not overflow. FIFO capacity is 256 bytes, the highest FIFO level is 256/4 = 64. If 200 ms is selected for FD\_TIME, FD\_SAMPLES would be equal to 128 and while sampling the FIFO at 200 ms. The FIFO would more than likely overflow creating loss of data since 128 samples (256 bytes) is the full depth of the FIFO. If the FIFO sampling frequency was reduced to 100 ms, the number of samples would be 64 (128 bytes), which is only half of the FIFO size then you will not have FIFO overflow. Therefore, to calculate the appropriate sample time, determine what will fill half of the FIFO or at most 2/3 of the FIFO and use that time as the sampling period.

#### Summary / Results

There are two modes for configuring the flicker function in this device, on-chip and data sampling. On-chip flicker detection uses an embedded algorithm and data sampling uses FIFO to access data. ams OSRAM provides a robust flicker detection functionality in many devices, the primary application for the flicker detection function would be flicker-immune camera operation. These efforts can make it easier to minimize flicker-induced problems.

#### **Revision Information**

- Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

- Correction of typographical errors is not explicitly mentioned.

## **Legal Information**

## Copyrights & Disclaimer

Copyright ams-OSRAM AG, Tobelbader Strasse 30, 8141 Premstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. Information in this document is believed to be accurate and reliable. However, ams-OSRAM AG does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Applications that are described herein are for illustrative purposes only. ams-OSRAM AG makes no representation or warranty that such applications will be appropriate for the specified use without further testing or modification. ams-OSRAM AG takes no responsibility for the design, operation and testing of the applications and end-products as well as assistance with the applications or end-product designs when using ams-OSRAM AG products. ams-OSRAM AG is not liable for the suitability and fit of ams-OSRAM AG products in applications and end-products planned. ams-OSRAM AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data or applications described herein. No obligation or liability to recipient or any third party shall arise or flow out of ams-OSRAM AG rendering of technical or other services. ams-OSRAM AG reserves the right to change information in this document at any time and without notice.

#### **RoHS Compliant & ams Green Statement**

RoHS Compliant: The term RoHS compliant means that ams-OSRAM AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories plus additional 4 substance categories (per amendment EU 2015/863), including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

ams Green (RoHS compliant and no Sb/Br/CI): ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material) and do not contain Chlorine (CI not exceed 0.1% by weight in homogeneous material).

#### **Important Information:**

The information provided in this statement represents ams-OSRAM AG knowledge and belief as of the date that it is provided. ams-OSRAM AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams-OSRAM AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams-OSRAM AG and ams-OSRAM AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

#### **Documents / Resources**

<u>ams TMD3719 Flicker Detection</u> [pdf] User Guide TMD3719 Flicker Detection, TMD3719, Flicker Detection, Detection

#### References

• **III Sensor Solutions** ams

- III Login | ams

- Login ams

- II Products | ams

- Login | ams

- II Sensor Solutions | ams

- In Contact us | ams OSRAM

- U Login | ams

- II Products | ams

- III Login | ams

- III Login | ams

Manuals+,