# **Actel SmartDesign MSS SPI Configuration User Guide**

Home » Actel » Actel SmartDesign MSS SPI Configuration User Guide

## Contents [ hide

- 1 Introduction

- **2 Configuration Options**

- **3 Port Description**

- 4 Documents /

- Resources

- 4.1 References

- **5 Related Posts**

# Introduction

The SmartFusion Microcontroller Subsystem (MSS) provides two SPI hard peripherals (APB\_0 and APB\_1 sub busses) with optional FPGA fabric slave select ports extension.

The actual behavior of each SPI instance must be defined at the application level using the SmartFusion MSS SPI Driver provided by Actel.

In this document, we describe how you can enable the MSS SPI instances and access the fabric slave select ports. For more details about the MSS SPI hard peripherals, please refer to the <u>Actel SmartFusion Microcontroller Subsystem User's Guide</u>.

# **Configuration Options**

Enabling/Disabling SPI Instances. On the MSS canvas, you need to enable (default) or disable each SPI instance

based on whether it is being used in your current application. Disabled SPI instances are held in reset (lowest power state) after the Actel system boot code is executed. Enabled SPI instances external ports – MSS I/Os – are also automatically configured by the Actel system boot code. Note that MSS I/Os allocated to a SPI instance are available to connect to MSS GPIOs if that SPI instance is disabled. Refer to the **MSS GPIO** configurator handbook for more details.

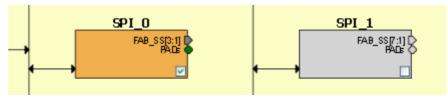

Figure 1: MSS SPI

Fabric Slave Select Extension. You may drive up to 3 slave select signals for SPI\_0 and 7 for SPI\_1 into the FPGA fabric; to do this, you need to manually promote to the top level the FAB\_SS[] port present on the MSS SPI instance(s) used in your application. You can then use the FAB\_SS port in the next level of hierarchy where it can be 'sliced' as individual slave select signals.

# **Port Description**

| Port Name       | Port Group | Direction | PAD? | Description                                                       |

|-----------------|------------|-----------|------|-------------------------------------------------------------------|

| DI              | PADs       | In        | Yes  | Shift data in (master or slave)                                   |

| DO              | PADs       | Out       | Yes  | Serial data out (generated by SPI as master)                      |

| CLK             | PADs       | Inout     | Yes  | Shift clock out (generated by SPI as master)                      |

| SS              | PADs       | Inout     | Yes  | External dedicated slave select port (generated by SPI as master) |

| FAB_SS[n:<br>1] |            | Out       | No   | Optional routed slave select ports (generated by SPI as master)   |

#### Notes:

- PAD ports are automatically promoted to top throughout the design hierarchy.

- Non-PAD ports must be promoted manually to the top level from the MSS configurator canvas to be available

as the next level of hierarchy.

Actel is the leader in low-power and mixed-signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at 5Hhttp://www.actel.com.

Actel Corporation 2061 Stierlin Court Mountain View, CA 94043-4655 USA

Phone 650.318.4200 Fax 650.318.4600

**Actel Japan**

EXOS Ebisu Building 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150, Japan Phone +81.03.3445.7671

Fax +81.03.3445.7668 6Hhttp://jp.actel.com

Actel Europe Ltd.

River Court, Meadows Business Park

Station Approach, Blackwater Camberley Surrey GU17 9AB

United Kingdom

Phone +44 (0) 1276 609 300 Fax +44 (0) 1276 607 540

**Actel Hong Kong**

Room 2107, China Resources Building

26 Harbour Road Wanchai, Hong Kong Phone +852 2185 6460

Fax +852 2185 6488

rax +002 2100 0400

www.actel.com.cn

© 2009 Actel Corporation. All rights reserved. Actel and the Actel logo are trademarks of Actel Corporation. All other brand or product names are the property of their respective owners.

#### **Documents / Resources**

### References

- •

• FPGAs and PLDs | Microchip Technology

- actel.com.cn

Manuals+, home privacy