# Actel SmartDesign MSS Cortex M3 Configuration User Guide

Home » Actel » Actel SmartDesign MSS Cortex M3 Configuration User Guide

SmartDesign MSS

Cortex<sup>™</sup> -M3 Configuration

User Guide

## **Contents**

- 1 Introduction

- **2 Configuration Options**

- **3 Port Description**

- 4 Documents /

Resources

- 4.1 References

- **5 Related Posts**

## Introduction

The SmartFusion Microcontroller Subsystem (MSS) contains an ARM Cortex-M3 microcontroller, a lowpower processor that features low gate count, low and predictable interrupt latency, and low-cost debug. It is intended for deeply embedded applications that require fast interrupt response features.

This document describes the ports that are available on the Cortex-M3 core in the SmartDesign MSS Configurator.

For more information about the specific implementation of the Cortex-M3 in the Actel SmartFusion device, please refer to the **Actel SmartFusion Microcontroller Subsystem User's Guide**.

## **Configuration Options**

There are no configuration options for the Cortex-M3 core in the SmartDesign MSS Configurator.

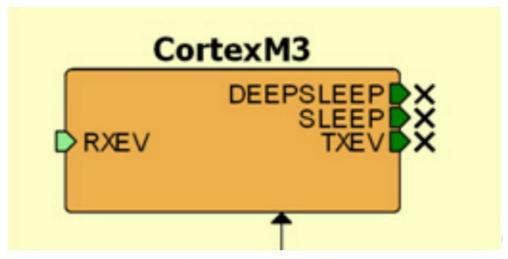

Figure 1: Cortex-M3 in SmartFusion

# **Port Description**

| Port Name | Direction | PAD? | Description                                                                                                                                                                      |

|-----------|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXEV      | In        | No   | Causes the Cortex-M3 to wake up from a WFE ( wait for event ) instruction. The event input, RXEV, is registered even when not waiting for an event, and so affects the next WFE. |

| TXEV      | Out       | No   | Event transmitted as a result of a Cortex-M3 SEV ( send event ) instruction. This is a single-cycle pulse equal to 1 FCLK period.                                                |

| SLEEP     | Out       | No   | This signal is asserted when the Cortex-M3 is in sleep now or sleep-on-exit mode, and indicates that the clock to the processor can be stopped.                                  |

| DEEPSLEEP | Out       | No   | This signal is asserted when the Cortex-M3 is in sleep now or sleep-on-exit mode when the SLEEPDEEP bit of the System Control Register is set.                                   |

## Note:

Non-PAD ports must be promoted manually to the top level from the MSS configurator canvas to be available as the next level of hierarchy.

Actel is the leader in low-power and mixed-signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at <a href="http://www.actel.com">http://www.actel.com</a>.

**Actel Corporation** 2061 Stierlin Court Mountain View, CA

94043-4655 USA Phone 650.318.4200

Fax 650.318.4600

**Actel Hong Kong**

United Kingdom

**Actel Europe Ltd.**

Room 2107, China Resources Building

River Court, Meadows Business Park

Station Approach, Blackwater

Camberley Surrey GU17 9AB

Phone +44 (0) 1276 609 300

Fax +44 (0) 1276 607 540

26 Harbour Road

Wanchai, Hong Kong

Phone +852 2185 6460

Fax +852 2185 6488

www.actel.com.cn

**Actel Japan**

EXOS Ebisu Building 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150, Japan Phone +81.03.3445.7671

Fax +81.03.3445.7668

http://jp.actel.com

© 2009 Actel Corporation. All rights reserved. Actel and the Actel logo are trademarks of Actel Corporation. All other brand or product names are the property of their respective owners.

## **Documents / Resources**

Actel SmartDesign MSS Cortex M3 Configuration [pdf] User Guide

SmartDesign MSS Cortex M3 Configuration, SmartDesign MSS, Cortex M3 Configuration, M3 Configuration

### References

- FPGAs and PLDs | Microchip Technology

- © actel.com.cn

Manuals+,