# **Actel SmartDesign MSS Configuration User Manual**

Home » Actel » Actel SmartDesign MSS Configuration User Manual

#### **Contents**

- 1 Actel SmartDesign MSS Configuration

- **2 Configuration and Connectivity**

- 3 Create the FPGA Fabric and AMBA

Subsystem

- **4 Memory Map Computation**

- **5 Product Support**

- 6 Documents / Resources

- **6.1 References**

- **7 Related Posts**

#### **Actel SmartDesign MSS Configuration**

#### **Actel Corporation, Mountain View, CA 94043**

© 2010 Actel Corporation. All rights reserved. Printed in the United States of America

Part Number: 5-02-00225-0 Release: November 2010

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

## **Trademarks**

Actel and the Actel logo are registered trademarks of Actel Corporation. Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc. All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

## **Configuration and Connectivity**

The SmartFusion Microcontroller Subsystem enables you to naturally extend the AMBA Bus into the FPGA fabric. You can configure the AMBA fabric interface as either APB3 or AHBLite depending on your design needs. A master and a slave bus interface is available in each mode.

This document provides the essential steps to creating mixed MSS-FPGA fabric AMBA AHBLite/APB3 system using the MSS configurator available in the Libero® IDE software.

AHBLite peripherals are connected to the MSS using CoreAHBLite version 3.0.112 or greater.

APB peripherals are connected to the MSS using CoreAPB3 version 3.0.101 or greater.

The CoreAHBLite and CoreAPB3 cores are bridged using CoreAHBtoAPB3 version 2.0.114 or greater.

For more details about the Fabric Interface Controller (FIC), please refer to the Actel SmartFusion Microcontroller Subsystem User's Guide.

#### **MSS Configuration**

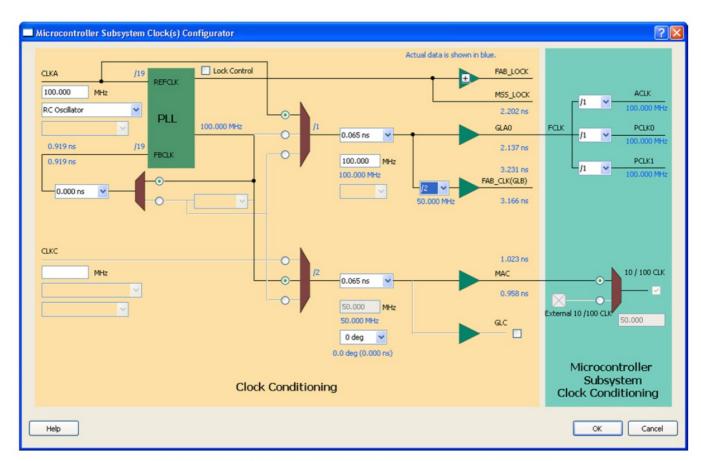

#### Step 1. Select the MSS FCLK (GLA0) to fabric clock clock ratio.

Select the FAB\_CLK divisor in the MSS Clock Management Configurator as shown Figure 1-1. You must perform post-layout static timing analysis to ensure that the design meets the timing requirements defined in the Clock Management Configurator. You may have to adjust the clock ratio between the MSS and the fabric to get a functional design.

Figure 1-1 · Select the MSS FCLK (GLA0) to Fabric Clock Clock Ratio

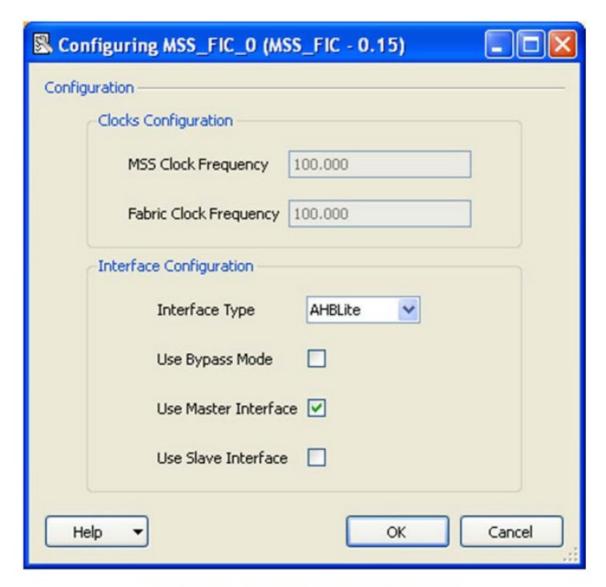

#### **Step 2.** Select the MSS AMBA mode.

Select the AHBLite Interface Type in the MSS Fabric Interface Configurator as shown in Figure 1-2.

Figure 1-2 · AHBLite Interface Selected

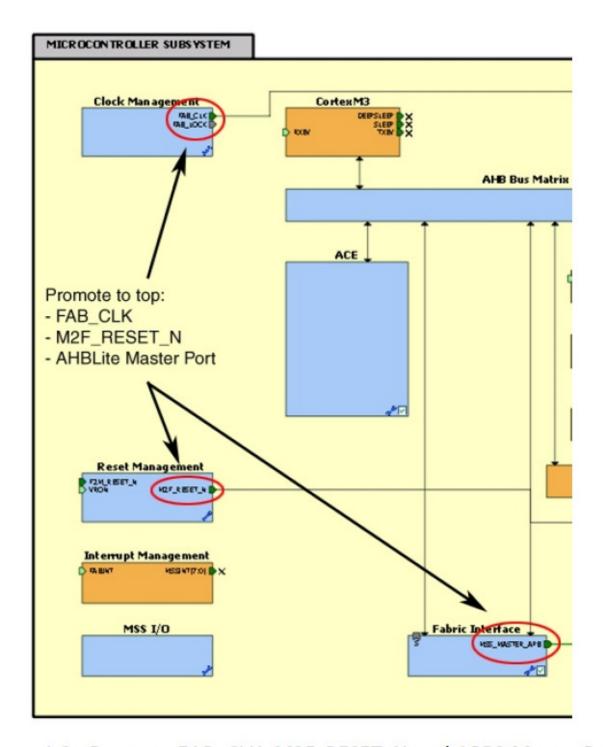

Step 3. Promote the Fabric Interface AHBLite Bus Interface (BIF) master port (as shown in Figure 1-3).

- Enable the AHBLite Master Bus Interface (BIF) as shown in Figure 1-2.

- In the MSS configurator, right-click the Bus Interface master port (MSS Fabric Interface core) and choose Promoteto- top. The BIF master port will then be available to the next level of hierarchy (where the fabric extension needs to be implemented).

#### **Step 4.** Promote FAB\_CLK to make it a port (as shown in Figure 1-3).

In the MSS configurator, right-click FAB\_CLK (MSS Clock Management core) and choose Clear attribute, then right-click it again and choose Promote-to-top. The FAB\_CLK port will then be available to the next level of hierarchy (where the fabric extension needs to be implemented).

**Note:** Actel recommends that you not change the FAB\_CLK top-level port name. The SmartDesign auto-connect feature only works if the FAB\_CLK port name has not been changed.

## **Step 5.** Promote M2F\_RESET\_N to make it a port.

In the MSS configurator, right-click M2F\_RESET\_N (MSS Reset Management core) and choose Clear attribute. The M2F\_RESET\_N port will then be available to the next level of hierarchy (where the fabric extension needs to be implemented).

**Note:** Actel recommends that you not change the M2F\_RESET\_N top level port name. The SmartDesign autoconnect feature only works if the M2F\_RESET\_N port name has not been changed.

Figure 1-3 · Promote FAB\_CLK, M2F\_RESET\_N and APB3 Master Port

## Create the FPGA Fabric and AMBA Subsystem

The fabric AMBA subsystem is created into a regular SmartDesign component, and then the MSS component is instantiated into that component (as shown in Figure 1-4).

## Step 1. Instantiate and configure CoreAHBLite.

• Select the Memory Mode 1 as shown in Figure 1-4. This mode provides 15 64KB slots that can be used to connect 15 AHBLite slaves. You may ignore the 16 4KB clients slots (mapped into Slot 4) and the huge slot as

they are irrelevant in this particular MSS master configuration.

• Enable the slots that you are planning on using for your application. Enable the slots from the ENABLE Master1 AHBLite Slave Slots group as shown in the figure below. Only slots 5 to 15 can be used when CoreAHBLite is connected to the MSS component. See the "Memory Map Computation" on page 13.

| Configuring CoreAHBLite_0 (CoreAHBLite - 3.0.112)                                 |              |                          |                          |          |

|-----------------------------------------------------------------------------------|--------------|--------------------------|--------------------------|----------|

| Configuration ————————————————————————————————————                                |              |                          |                          |          |

| Memory Configuration (slots = AHBLite slave slots, clients = Init/Config clients) |              |                          |                          |          |

| Me                                                                                | mory Mode: M | ode 1: 15 64KB slots, 1: | 6 4KB clients, 1 huge sl | ot 💌     |

| ENABLE Master0 AHBLite Slave Slots                                                |              |                          |                          |          |

| Slot                                                                              | 0:           | Slot 1:                  | Slot 2:                  | Slot 3:  |

| Slot                                                                              | 4:           | Slot 5:                  | Slot 6:                  | Slot 7:  |

| Slot                                                                              | 8: 🗌         | Slot 9:                  | Slot 10:                 | Slot 11: |

| Slot                                                                              | 12:          | Slot 13:                 | Slot 14:                 | Slot 15: |

| Hug                                                                               | e Slot:      |                          |                          |          |

| ENABLE Master1 AHBLite Slave Slots                                                |              |                          |                          |          |

| Slot                                                                              | 0:           | Slot 1:                  | Slot 2:                  | Slot 3:  |

| Slot                                                                              | 4:           | Slot 5: ☑                | Slot 6: 🗹                | Slot 7:  |

| Slot                                                                              | 8:           | Slot 9:                  | Slot 10:                 | Slot 11: |

| Slot                                                                              | 12:          | Slot 13:                 | Slot 14:                 | Slot 15: |

| Hug                                                                               | e Slot:      |                          |                          |          |

Figure 1-4 · Configuring AHBLite: Memory Mode and Slave Slots

Step 2. Instantiate Core AHB to APB3

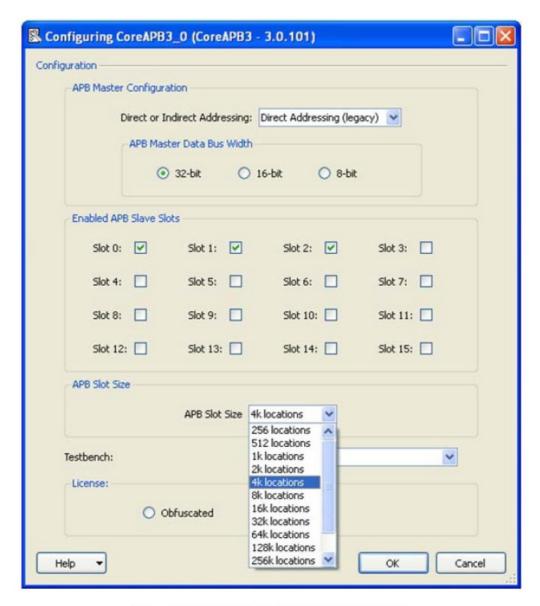

Step 3. Instantiate and configure CoreAPB3

- Select the direct addressing mode.

- Select the 32-bit APB bus master data bus width. It is the width of the MSS AMBA data bus width.

- Disable the slots that you do not plan on using for your application. All slots are available. See the "Memory Map Computation" on page 13 for more details about slot sizes and slave/slot connection.

- Select the APB slot size as 4KB or below as shown in Figure 1-5. Assuming that you have selected 64KB slot sizes for CoreAHBLite, then the maximum size of the slots on CoreAPB3 (16 slots) is 64KB/16 = 4KB when going through CoreAHBtoAPB3.

Figure 1-5 · Select the APB Slot Size

- **Step 5.** Instantiate and configure AMBA AHBLite and APB peripherals in your design.

- **Step 6**. Connect the subsystem together. This can be done automatically or manually.

**Automatic Connection** – The SmartDesign auto-connect feature (available from the SmartDesign Menu, toolbar or by right-clicking the Canvas) will automatically connect the subsystem clocks and resets and present you with a memory map editor where you can assign the AHBLite and APB slaves to the proper addresses. Note that the auto-connect feature performs the clock and reset connections only if the FAB\_CLK and M2F\_RESET\_N port names have not been changed on the MSS component.

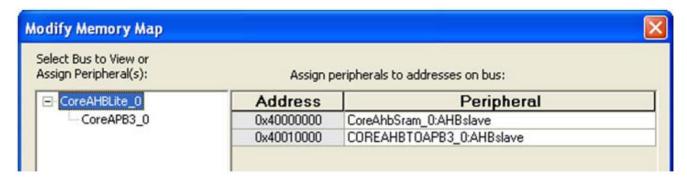

Figure 1-6 · SmartDesign Memory Map Editor - AHBLite Slaves

## **Configuration and Connectivity**

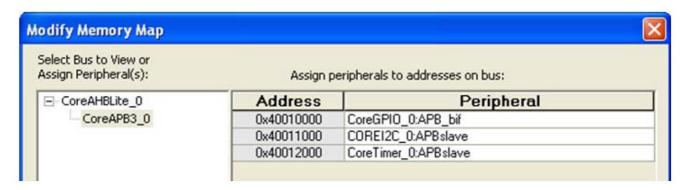

Figure 1-7 · SmartDesign Memory Map Editor - APB Slaves

## Manual Connection- Connect the subsystem as follows:

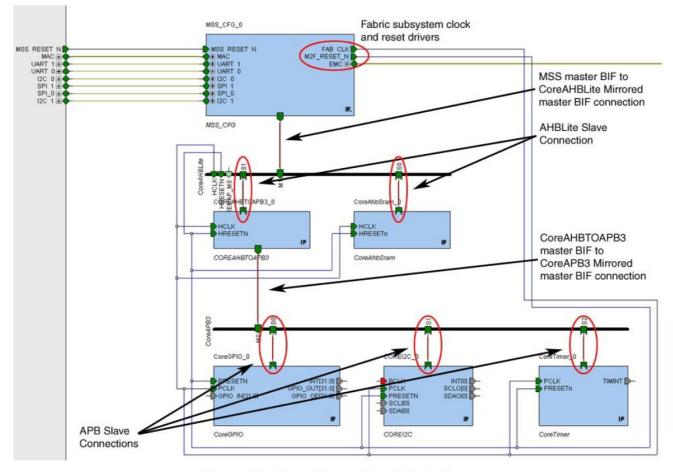

- Connect the CoreAHBLite mirrored-master BIF M0 or M1 to the MSS Master BIF (as shown in Figure 1-8).

Use M1 if you plan to create a multi-master subsystem where you have a master in the fabric that requires the remap feature and thus needs to be connected to M0.

- Connect the slave BIF of CoreAHBtoAPB3 to the mirrored slave BIF of CoreAHBLite.

- Connect the CoreAPB3 mirrored-master BIF to the MSS master BIF.

- Connect the APB and AHBLite slaves to the proper slots as per your memory map specification.

- Connect FAB CLK to HCLK/PCLK of all AHBLite/APB peripherals in your design.

- Connect M2F\_RESET\_N to HRESET/PRESET of all AHBLite/APB peripherals in your design.

Figure 1-8 · Manual Connections in Subsystem

## **Memory Map Computation**

## **General Formula**

For AHBLite, the slot size is always 64KB slots = 65536 slots (0x10000).

For each AHBLite slots 5 to 15 (slots 0 to 4 are prohibited as per the CortexM3 memory map), the address of the client peripheral is:

0x40000000 + (AHBLite slot number \* 0x10000).

## For each APB3 slots (all slots available), the address of the client peripheral is:

0x40000000 + (AHBLite slot number \* 0x10000) + (APB3 slot number \* APB3 slot size).

**Note**: The base address for the fabric is fixed at 0x4005000, but to simplify the memory map equation we are showing the base address as 0x40000000.

#### **Memory Map View**

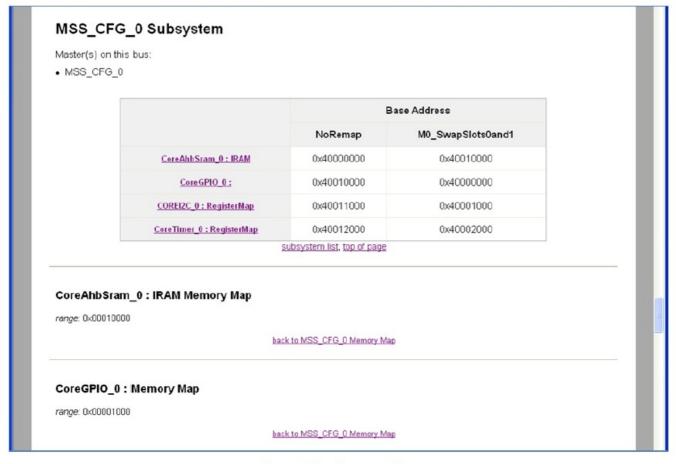

You can see the system memory map by using the SmartDesign Memory Map / Data Sheet feature (from the SmartDesign menu in the Libero IDE Project Manager). For example, Figure 2-1 is the memory map generated for the subsystem shown in Figure 1-8 on page 11.

Figure 2-1 · Memory Map

#### **Product Support**

Actel backs its products with various support services including Customer Service, a Customer Technical Support Center, a web site, an FTP site, electronic mail, and worldwide sales offices. This appendix contains information about contacting Actel and using these support services.

#### **Customer Service**

- Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From Northeast and North Central U.S.A., call 650.318.4480

- From Southeast and Southwest U.S.A., call 650. 318.4480

- From South Central U.S.A., call 650.318.4434

- From Northwest U.S.A., call 650.318.4434

- From Canada, call 650.318.4480

- From Europe, call 650.318.4252 or +44 (0) 1276 401 500

- From Japan, call 650.318.4743

- From the rest of the world, call 650.318.4743

- Fax, from anywhere in the world 650.318.8044

#### **Actel Customer Technical Support Center**

Actel staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions. The Customer Technical Support Center spends a great deal of time

creating application notes and answers to FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

#### **Actel Technical Support**

Visit the Actel Customer Support website (<a href="www.actel.com/support/search/default.aspx">www.actel.com/support/search/default.aspx</a>) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the Actel web site.

#### Website

You can browse a variety of technical and non-technical information on Actel's home page, at www.actel.com

#### **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center from 7:00 A.M. to 6:00 P.M., Pacific Time, Monday through Friday. Several ways of contacting the Center follow:

#### **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request. The technical support email address is <a href="tech@actel.com">tech@actel.com</a>

#### **Phone**

Our Technical Support Center answers all calls. The center retrieves information, such as your name, company name, phone number and your question, and then issues a case number. The Center then forwards the information to a queue where the first available application engineer receives the data and returns your call. The phone hours are from 7:00 A.M. to 6:00 P.M., Pacific Time, Monday through Friday. The Technical Support numbers are:

650.318.4460 800.262.1060

Customers needing assistance outside the US time zones can either contact technical support via email (<a href="mailto:tech@actel.com">tech@actel.com</a>) or contact a local sales office. Sales office listings can be found at <a href="https://www.actel.com/company/contact/default.aspx">www.actel.com/company/contact/default.aspx</a>

Actel is the leader in low-power and mixed-signal FPGAs and offers the most comprehensive portfolio of system and power management solutions. Power Matters. Learn more at <a href="https://www.actel.com">www.actel.com</a>

#### **Actel Corporation**

- 2061 Stierlin Court

- Mountain View, CA 94043

- USA Phone 650.318.4200

- Fax 650.318.4600

- Customer Service: 650.318.1010

- Customer Applications Center: 800.262.1060

## Actel Europe Ltd.

River Court, Meadows Business Park

- Station Approach, Blackwater

- Camberley Surrey GU17 9AB

- United Kingdom Phone +44 (0) 1276 609 300

- Fax +44 (0) 1276 607 540

## **Actel Japan**

- EXOS Ebisu Building 4F

- 1-24-14 Ebisu Shibuya-ku

- Tokyo 150

- Japan

Phone +81.03.3445.7671

- Fax +81.03.3445.7668

- http://jp.actel.com

## **Actel Hong Kong**

- · Room 2107, China Resources Building

- 26 Harbour Road

- Wanchai

- Hong Kong Phone +852 2185 6460

- Fax +852 2185 6488

- www.actel.com.cn

## **Documents / Resources**

Actel SmartDesign MSS Configuration [pdf] User Manual

How to Create a MSS and Fabric AMBA AHBLite APB3 Design, SmartDesign MSS Configuration, SmartDesign MSS, Configuration

## /Actel

#### References

- S FPGAs and PLDs | Microchip Technology

- © actel.com.cn

- •

• FPGAs and PLDs | Microchip Technology

- •

• FPGAs and PLDs | Microchip Technology

- •

• FPGAs and PLDs | Microchip Technology

- FPGAs and PLDs | Microchip Technology

Manuals+.